# MR. OPERATOR

We would advise you of the importance of reading this Manual, which will help you to obtain the very best efficiency in our electronic Pin-Ball.

RECEL S.A.

HNOS. G? NOBLEJAS, 39 MADRID-17 SPAIN TELEF 2679395 & 4074800 TELEX 42327 RECEL E

- REPRESENTATIVES IN -

Aruba, Neth. Ant.

France

Portugal

Australia

Holland

South Africa

Austria

Hong Kong

Sweden

Belgium

Hungary

Switzerland

Brazil

Italy

United Kingdom

Canada

Japan

United States

Colombia

Lebanon

West Germany

Denmark

Norway

Yugoslavia

España

New Caledonia

|   |        |     |         | ^   | <br>-   |

|---|--------|-----|---------|-----|---------|

| • | I OCAL | HEP | HH (")H | VIA | <br>/r- |

### - NOTE -

RECEL S.A. reserves the right to change whatever specification of its product that it sees fit without prior notification.

RECEL S.A. assumes no responsibility as to the use of the information contained in this manual.

# **CONTENTS**

| SECTION |                                                                                                                                                                            | PAGE                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| 1 .     | GENERAL INFORMATION  1.1 FOREWORD  1.2 PURPUSE OF THE MANUAL  1.3 LAYOUT OF THE MANUAL  1.4 GENERAL CHARACTERISTICS  1.5 EXPRESSIONS                                       | 1-1<br>1-1<br>1-1<br>1-2<br>1-4                        |

| 2       | BASIC CONCEPTS  2.1 SIMPLIFIED STRUCTURE  2.2 BASIC REAL STRUCTURE  2.3 REAL STRUCTURE  2.4 STRUCTURE OF SYSTEM III  2.5 PHILOSOPHY OF SYSTEM III                          | 2-1<br>2-4<br>2-5<br>2-7<br>2-9                        |

| 3       | DESCRIPTION 3.1 GENERAL FUNCTIONS 3.2 SELF-CHECK 3.3 REPRESENTATION AREAS 3.4 HANDICAP 3.5 ADJUSTMENT 3.6 LOGIC DETECTOR 3.7 MINI-PRINTER 3.8 SIMULATION SYSTEM III        | 3-1<br>3-1<br>3-4<br>3-6<br>3-6<br>3-8<br>3-11<br>3-11 |

| 4       | MAINTENANCE 4.1 GENERAL CONSIDERATIONS 4.2 COILS 4.3 LAMPS 4.4 CONTACTS 4.5 MACHINE DIAGRAM                                                                                | 4-1<br>4-1<br>4-2<br>4-2<br>4-3                        |

| 5       | MODULES  5.1 POWER SUPPLY AND SOUND  5.2 MASTER UNIT  5.3 DISPLAY CONTROL UNIT  5.4 DISPLAYS  5.5 TILT UNIT  5.6 ILLUMINATION AND CABINET USE  5.7 MULTIPLEXER—DRIVER UNIT | 5-1<br>5-5<br>5-15<br>5-20<br>5-24<br>5-25<br>5-26     |

| 6       | TIMING AND PIN-OUT                                                                                                                                                         |                                                        |

| 7       | RAM MEMORY MAR                                                                                                                                                             |                                                        |

## **SECTION 1**

### GENERAL INFORMATION

#### 1.1 FÖREWORD

"SYSTEM III" represents the most advanced application of electronics technology in the pin-ball industry. Its performance betters all previous system possibilities with surprising simplicity, offering in addition such a quantity of information that opens up a new era in the coin operated games, thus allowing a strict and programmed control over the performance of every machine in all aspects (coin collection, faults, game behaviour, timing, etc).

All the information supplied by the machine (which is printed out) can be fed into a main computer, which will file and process all data, giving out percentages, averages, statistics, and which will activate an alarm when some parameter suffers a deviation greater than the set values.

With "SYSTEM III" we have obtained a pin-ball in which all units are interchangeable from one model to another, irrespective of whether it is a single, two or four player version. The only differences you will find between one model and another are the following: (1) the playfield; (2) the actual decoration; and (3) the game memory (which is mounted in the Master Unit, with socket).

#### 1.2 PURPOSE OF THIS MANUAL

In this Manual we have described the characteristics, handling and maintenance of our "SYSTEM III". It has been written with existing pinball technical staff in mind, who might not yet be familiar with microprocessor technology.

This manual is intended to give a very simple understanding of our "SYSTEM III" and its general application to pin—ball machines, and here we are not going to deal with the particular characteristics of any given model, as these will be given in the respective service manual.

#### 1.3 LAYOUT OF THE MANUAL

The contents of sections 2, 3, 4, 5, 6 and 7 are as follows:

Section 2: Basic Concepts, is the heading for an elementary and brief introduction to the microprocessor technology. Its only purpose is to provide some general guide—lines to those technicians who have not yet come into contact with data processing electronic systems.

- Section 3: Describes the main characteristics of the System: Self-Check,

Representation areas, Handicaps, Adjustment, Logic Detector,

Mini-printer and Simulation System.

- Section 4: This section is dedicated to an analysis of the essentially electrical parts: coils, lamps and contacts. It also includes a general schematic of the System.

- Section 5: This comprises a full description of all the units within the System, an explanation of the functioning of each of these units and theoretical, practical and connection diagrams for such units.

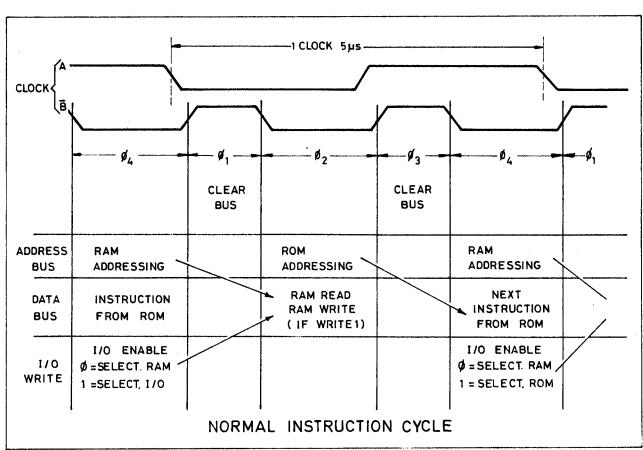

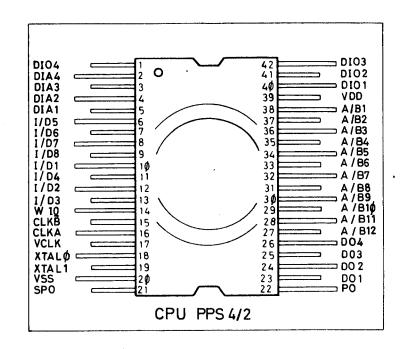

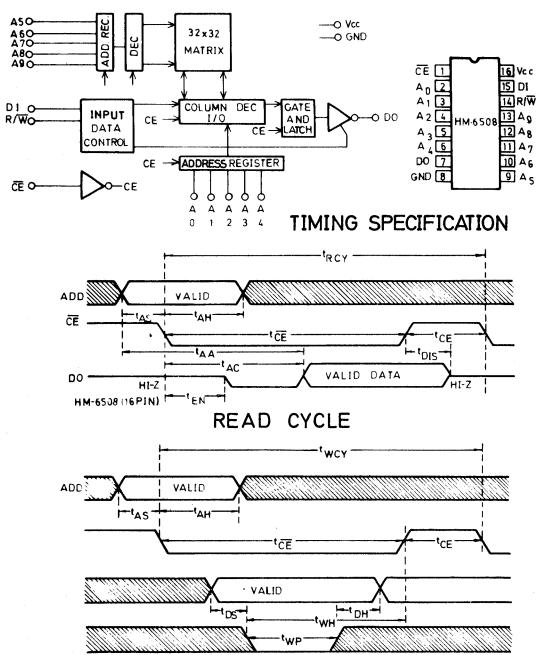

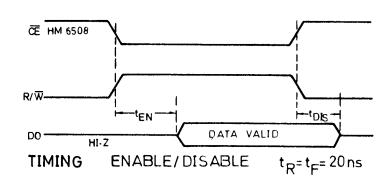

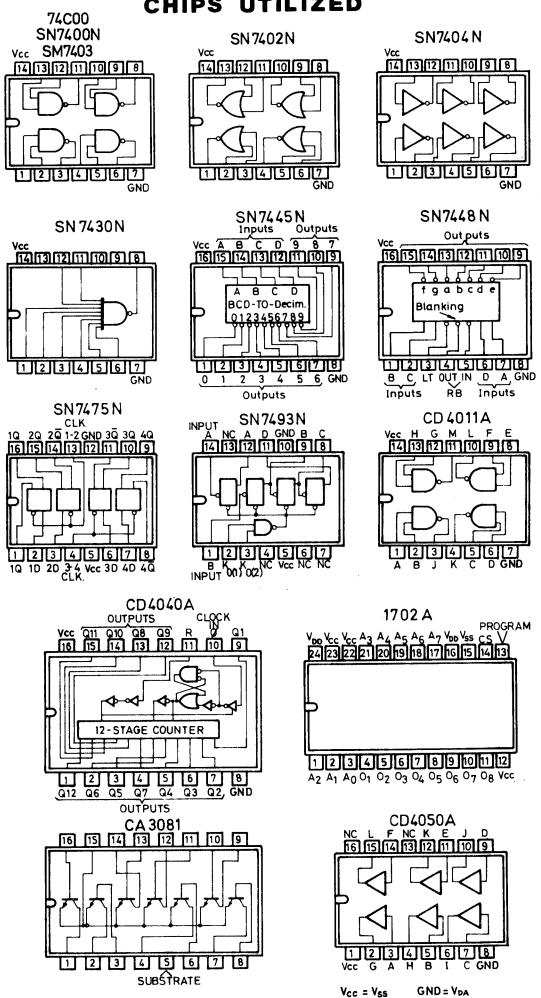

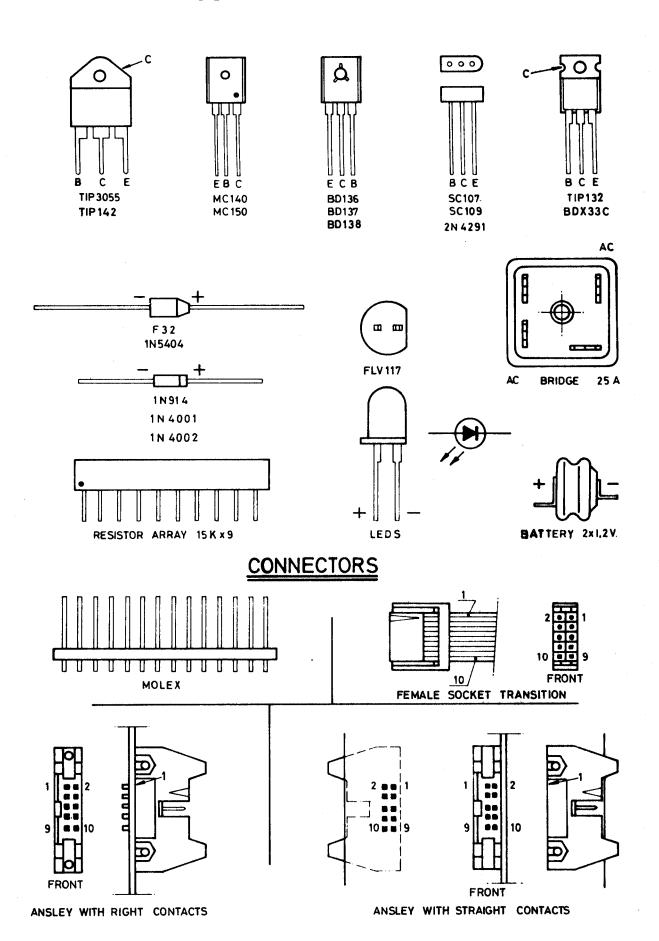

- Section 6: This presents a basic time diagram for the LSI MOS and RAM C-MOS chips, as well as the PIN-OUT for all the chips and components used.

- Section 7: This is firstly a map summarising the organization of the RAM memory, and a representation in full detail of all the display indications in the various representation areas.

#### 1.4 GENERAL CHARACTERISTICS

- \* Processor in use: ROCKWELL PPS-4

- \* Intelligent system assembled on just 1 (one) module.

- \* General wiring system: flat tape

- \* Data memory maintained when the machine is switched off

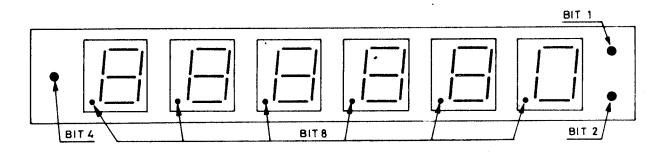

- \* 4 counters of  $6\frac{1}{2}$  digits

- \* Different handicap (highest score) for each player

- \* 3 and 5 balls

- \* 3 adjustable coin rejectors

- \* Electronic digital sound

- \* 2 types of game with extra play

- \* 3 types of game with extra ball

- \* Limit on extra play = 9 (separate from credit display)

- \* Limit on extra ball = 9 (with display for this use)

- \* Credit limit adjustable from 9 through 99

- \* Electronic match number

- \* Adjustments and rules contained in memory (without switches)

- \* Model and serial number register

- \* Register code of the last printer used for coin collection

- \* Date or number register of last coin collection

- \* "Game Over" time register

- \* "Machine in Play" time register

- \* Coin meter for 1st coin rejector

- \* Coin meter for 2nd coin rejector

- \* Coin meter for 3rd coin rejector

- \* Extra Ball meter

- \* Extra Game meter

- \* Total Service meter

- \* Total Play meter

- \* 4 extra meters for use in the game or for any other use

- \* Display representation of all the above mentioned data

- \* Print-out of all data on portable mini-printer

- \* Charge and/or zeroing of registers and meters with mini-printer

- \* Data collected with mini-printer can be fed to central computer

- \* Cabinet with "fold-down" head (without disconnecting)

- \* All units interchangeable from one model to another

- \* Alteration and/or zeroing of registers and meters by printer

- \* Power supply (adjustable): 100-120-135-150-200-220-240-260 v. (50 60 Hz)

- \* Consumption: 110 watts (at rest)

280 watts (maximum, in play)

- \* Playfield inclination:  $5^{\circ}$   $10^{\circ}$  (adjustable)

- \* Dimensions when mounted: 1190 mm deep

650 mm wide

1780 mm high

\* Dimensions in transport: 1315 mm deep

670 mm wide

580 mm high

- \* Nett weight: 91 kgs.

- \* Gross weight: 105 kgs.

#### 1.5 EXPRESSIONS

In order to understand this Manual more easily, we define herebelow some of the principal terms and expressions.

```

Ø (Low) ....

Logic level of a power point or register R \leq 0.6 volts

Logic level of a power point or register R \geqslant 3 volts

1 (High) ...

OPEN ..... Logic level between High and Low

PULSE ..... Interval from which a level changes to another and returns

to the original level

Line, instruction or fact of setting "HIGH" in a point or

SET .....

register

RESET .....

Line, instruction or fact of setting "LOW" in a point or

register

CLOCK .....

Line with repetitive pulses used as a time base, or pulse

that defines the instant when an effect should take place

ENABLE ....

Form of allowing something to realize a certain function

DATA ..... Line or lines via which data are transmitted or received

BUS ...... Group of lines used by all the circuits connected to it

BUFFER .... Chips used as protection and interface between the MOS

circuits and the TTL and Drivers.

INVERTER ... Chip whose logic function is defined by f = A

Chip whose logic function is defined by f = A.B.C.-.-.-

AND ....

NAND ..... Chip whose logic function is defined by f = \overline{A_{\bullet}B_{\bullet}C_{\bullet-\bullet-\bullet}}

OR ...... Chip whose logic function is defined by f = A + B + -

NOR ...... Chip whose logic function is defined by f = A + B + -

INTERFACE .. Circuit which makes two different circuits compatible in

level or form of working

Random Access Memory (variable data)

RAM .....

ROM ....

Read Only Memory (instructions and constants)

Electric Programmable Read Only Memory

EPROM ....

CPU .....

Central Processing Unit

DRIVER .... Output interface (generally 1 transistor)

TTL ..... Transistor (IN) Transistor (OUT) Logic

PMOS ...... Positive Metal Oxide Semiconductor

Negative Metal Oxide Semiconductor

NMOS .....

CMOS ..... Complementary Metal Oxide Semiconductor

Input-Output

I/O .....

PIO ..... Programmable Input-Output

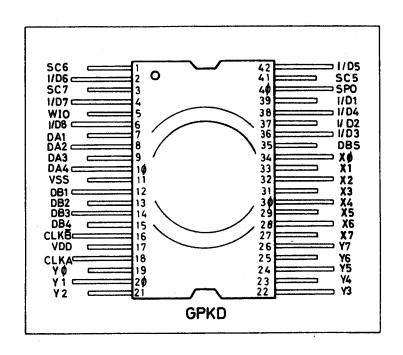

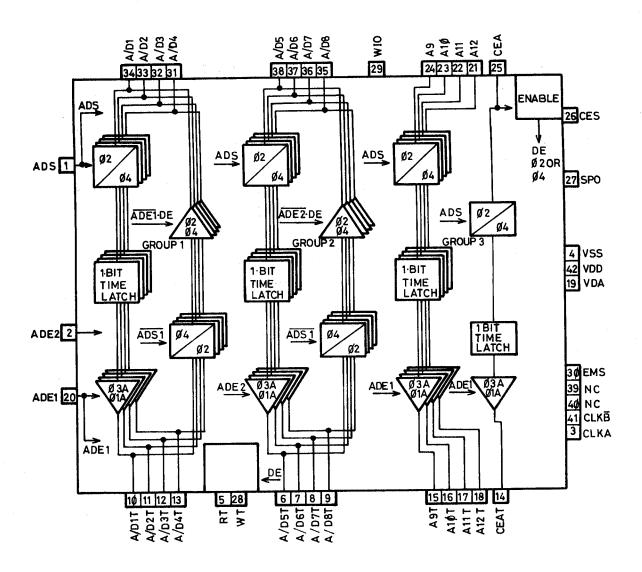

GPKD ..... General Processor Keyboard and Display

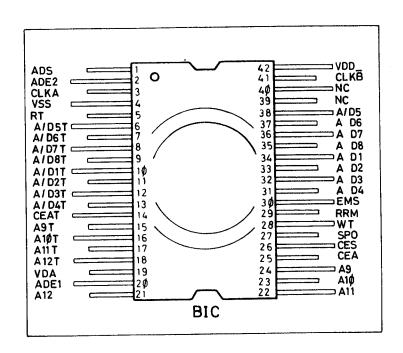

BIC ..... BUS interface circuit

```

## **SECTION 2**

## **BASIC CONCEPTS**

### 2.1 SIMPLIFIED STRUCTURE

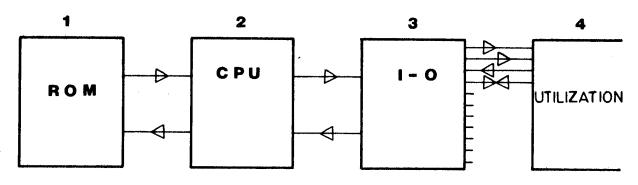

Basically the most simple lay—out involving a micro—processor system will be as depicted in the block diagram shown below :-

Fig. 2.1

The operation of such a system would be equivalent to a sequence circuit in which a control circuit 2 (CPU) alters the outputs from 3 (I/O) in accordance with a stored sequence in the program memory 1 (ROM).

The circuit 1 program memory contains the code for all those instructions received in circuit 2 (CPU), by which means it is able to process the data and transfer the results to circuit 3 (I/O) which in turn controls the coils, lamps and/or other parts of the system (4).

In order to see more clearly the basic operation, let us assume a very simple micro-processor system, as illustrated in Fig. 2.1:

Chip  $N^{\circ}$  1 (ROM) contains the combinations (or codes of 4 bits for example) that Chip  $N^{\circ}$  2 (CPU) receives in sequence, bearing in mind that Chip  $N^{\circ}$  1 is controlled by the same CPL (logic unit which interprets the instructions contained in ROM, and carries them out controlling the memories and peripherals). These codes are recorded, logically in binary, and each set of them (each word or 'byte') expresses a specific instruction.

Chip Nº 2 (CPU) interprets each one of these combinations (instructions) and makes a SET, RESET or READING of any input from circuit 3 (I/O).

As each word (or byte) sent by the ROM to the CPU, contains 4 bits, there are 16 possible and different combinations (instructions) which are as follows:-

| HEXAD. | INSTRUCTION |     | CPU FUNCTION                    | MNEMONIC   |

|--------|-------------|-----|---------------------------------|------------|

| ø      | 0000        |     | SET in all outputs              | <b>SO</b>  |

| 1      | 0001        |     | SET in output 1                 | S1         |

| 2      | 0010        |     | SET in output 2                 | 52         |

| 3      | 0011        |     | SET in output 3                 | 53         |

| 4      | 0100        |     | SET in output 4                 | <b>S</b> 4 |

| 5      | 0101        |     | RESET in output 1               | R1         |

| 6      | 0110        |     | RESET in output 2               | R2         |

| 7      | 0111        |     | RESET in output 3               | R3         |

| 8      | 1000        |     | RESET in output 4               | R4         |

| 9      | 1001        | (*) | Skip if input 1 is High         | SK1        |

| Α      | 1010        |     | Skip if input 2 is High         | SK2        |

| В      | 1011        |     | Skip if input 3 is High         | SK3        |

| С      | 1100        |     | Skip if input 4 is High         | SK4        |

| Đ      | 1101        |     | Advance as many instructions as | ,          |

|        |             |     | indicated by the following      |            |

|        |             |     | word                            | T+X        |

| E      | 1110        |     | Go back as many words as per    |            |

|        |             |     | the value of the following      |            |

|        |             |     | instruction                     | T-X        |

| F      | 1111        |     | RESET all outputs               | RO         |

(\*) Ignore the following instruction if the given condition is complied with (Skip).

Fig. 2.2

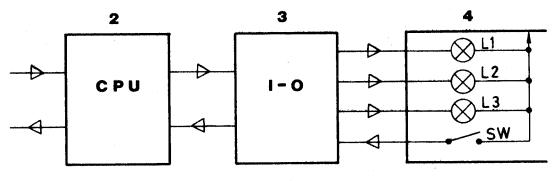

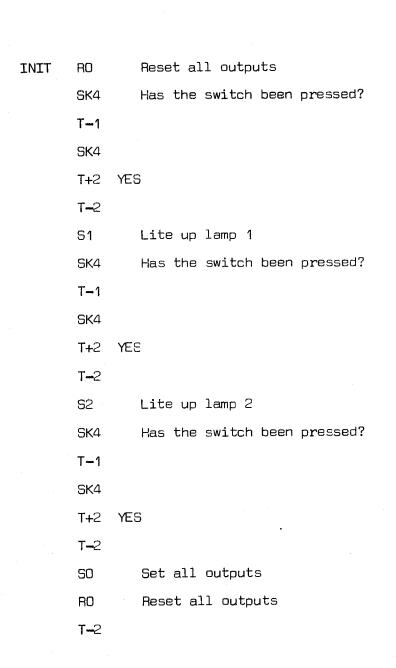

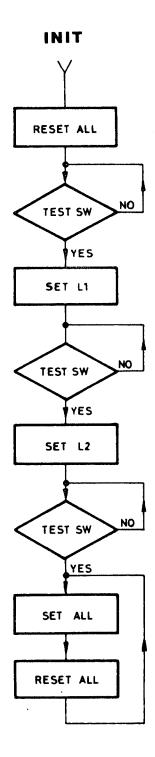

Assuming that we have this simplified system, we can now use it in the set—up shown under Fig. 2.2, and can make the following program.

The program will lite up the first lamp on pressing the switch (in 4) for the first time, the 2nd lamp will be lit up after pressing the switch for the second time, and with the 3rd press all three lamps will be flashing.

With these instructions translated into binary code (according to the previous table) and recorded in the ROM memory, the program will carry out the prescribed steps, liteing up L1, then L2 and then flashing all 3 lamps.

Fig. 2.3

#### 2.2 REAL BASIC STRUCTURE

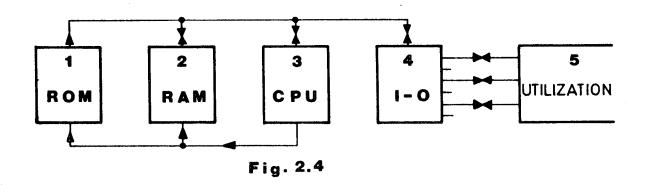

We can now consider the real structure of a simple system using microprocessors (Fig. 2.4); here we have also added something new - the RAM memory.

Analysis of the system:

- ROM (1) Read Only Memory contains the program which is interpreted by the CPU which in turn will make or introduce data into the RAM memory or alter and read the inputs and outputs from the I/O (4), controlling by these latter, all the parts in UTILIZATION (5) (e.g. relays, motors, lamps, etc.). The ROM memory is recorded during manufacture and cannot be changed.

- RAM (2) Random Access Memory is the memory that the CPU uses to store all types of data (final or intermediate), subsequently making operations or alterations on the data and transferring these to the I/O outputs during the program run. This memory serves therefore as a variable data store for the CPU because this unit requires a large data stock capacity.

- CPU (3) Central Processing Unit interprets the program and carries out all the operations and movements indicated in the program. The CPU incorporates registers, accumulators, counters, decoders and multiplexers required to control and direct the memories and peripherals.

- I/O (4) Input/Output, a circuit which controls the external systems (indicators, motors, read-out and other peripherals) as directed by the CPU. Depending on the number of lines that the Utilization section (5) requires, there will be a need for the same number (1, 2 or "x") of I/O circuits (peripherals). These circuits can provide lines that would be outputs, inputs and both at the same time.

- UTILIZATION (5) This is an assembly of all those parts which the system needs in particular to operate. These parts could be other electronic circuits, read-outs or electrical or electromechanical receivers, loads of any type (with their drivers and respective interfaces) etc. etc.

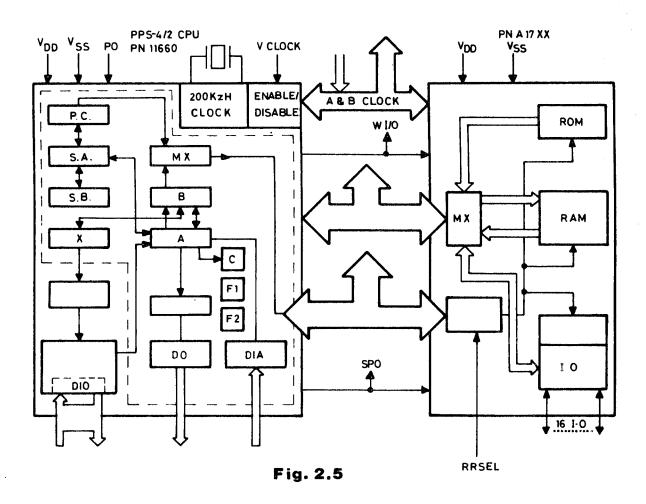

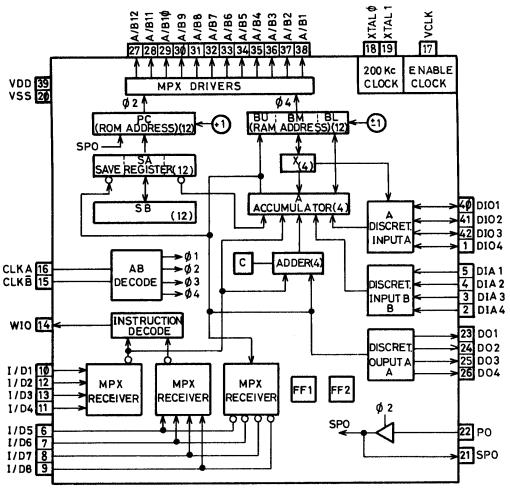

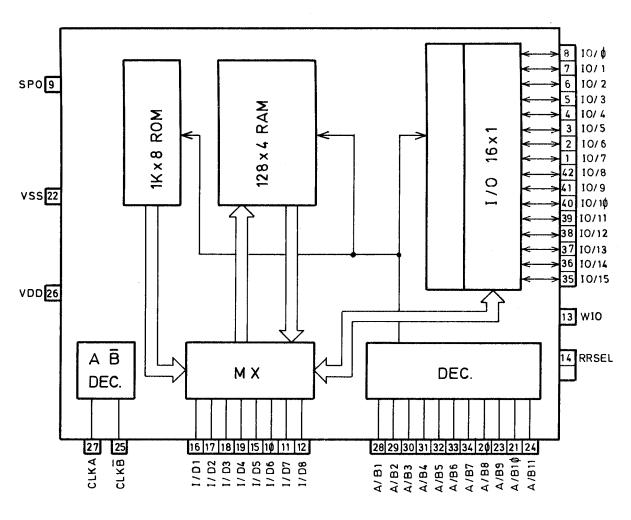

In Fig. 2.5 we can see a simple but real system the layout of which requires only two (2) chips.

The more important registers have been depicted on the CPU chip. "A" is the main working register (accumulator), through which all data from RAM, I/O, DO, DIA, etc., pass and where all types of logical and arithmetical operations are performed. "B" is the register that contains the address of the RAM, which can be read or altered. "P.C." (program counter) is the register that addresses the ROM memory (program). "S.A. and S.B" are registers that enable the program counter (P.C.) contents to be stored, to carry out any sub-routine (situated somewhere else in the program) and come back to the main program, restoring the P.C. contents. "D.O., DIA and DIO" are system inputs and outputs incorporated in the CPU chip.

The second chip contains the ROM, RAM memories and an I/O circuit with 16 inputs/outputs.

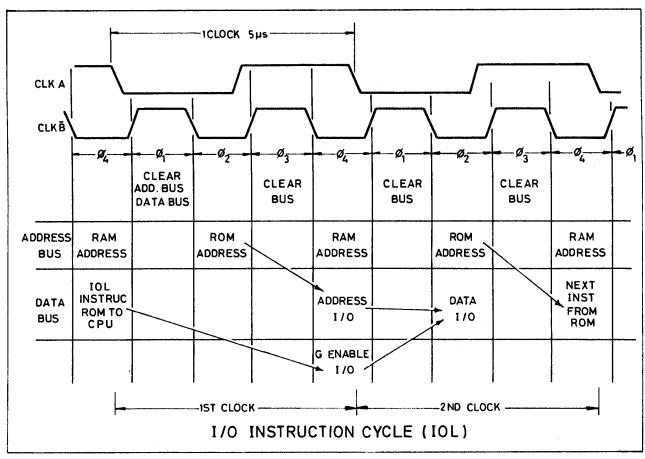

As we can see, this assembly made up of two chips, contains all the basic parts required to control and manipulate data, hence the number of chips is not the significant factor (the system could be of just one), everything depending on the number of functions incorporated in the chip or chips and of course, the maximum capacity of them (ROM memory and RAM memory capacity, number of inputs/outputs, and CPU instruction power) and the time required to carry out a specific instruction or movement; in our case, the movement of a clock taking 5 µsecs.

## DECIMAL/HEXADECIMAL/BINARY TABLE

| DECIMAL | HEXADE-<br>CIMAL | DISPLAY<br>PRES. | BINARY |      | DECIMAL | HEXADE-<br>CIMAL | DISPLAY<br>PRES. | BINARY |

|---------|------------------|------------------|--------|------|---------|------------------|------------------|--------|

|         |                  |                  | DCBA   |      |         |                  |                  | DCBA   |

| 0       | 0                |                  | 0000   |      | 8       | 8                |                  | 1000   |

| 1       | 1                |                  | 0001   |      | 9       | 9                |                  | 1001   |

| 2       | 2                |                  | 0010   |      | 10      | А                |                  | 1010   |

| 3       | 3                |                  | 0011   |      | 11      | В                |                  | 1011   |

| 4       | 4                |                  | 0100   | 94.5 | 12      | С                |                  | 1100   |

| 5       | 5                | 5                | 0101   |      | 13      | D                |                  | 1101   |

| 6       | 6                | 6                | 0110   |      | 14      | Ε                |                  | 1110   |

| 7       | 7                |                  | 0111   |      | 15      | F                |                  | 1111   |

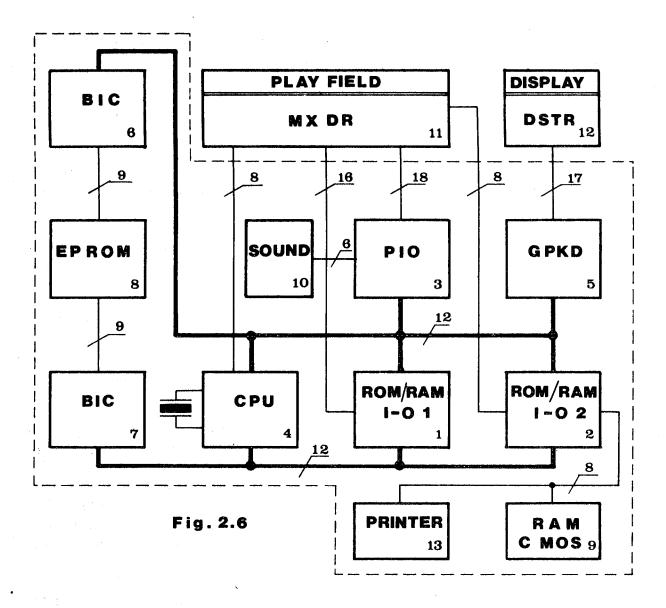

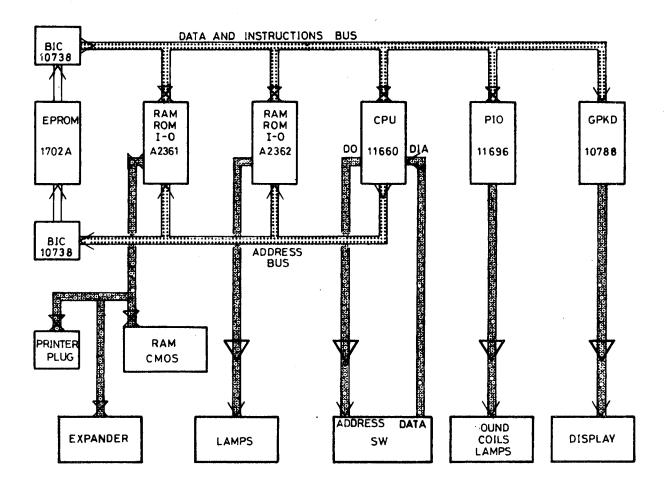

With reference to Fig. 2.6 and following the order of the numbering shown for each chip or unit, we will now briefly define the functions that they carry out.

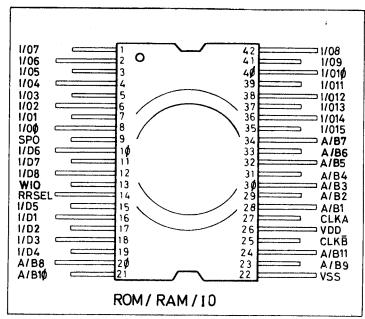

- 1. ROM/RAM I=0 1 This chip consists of 3 parts: a) ROM which contains the first 1000 program bytes (words of 8 bits);

- b) RAM containing the first 128 data bytes (words of 4 bits); c) I/O 16 outputs used as registers for the playfield.

- 2. ROM/RAM I=0 2 This is a chip the same as (1) but containing: a) ROM with the 2nd 1000 program bytes; b)RAM with the 2nd 128 data bytes; c) I/O with 8 outputs which can be used as registers for the playfield and 8 outputs controlling the RAM CMOS memory and products.

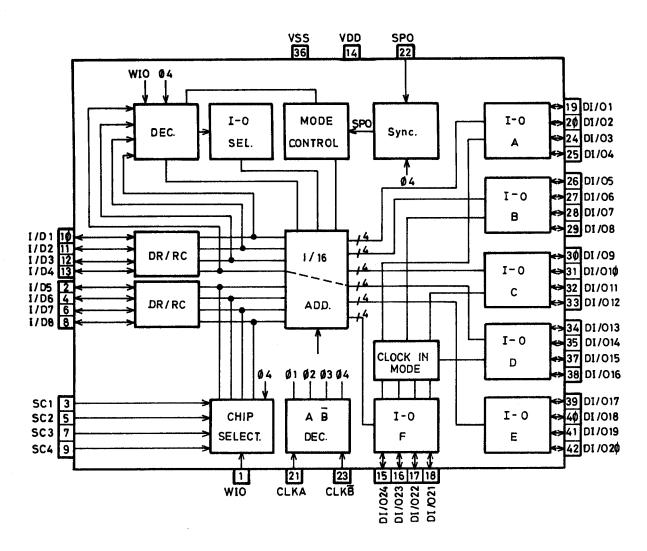

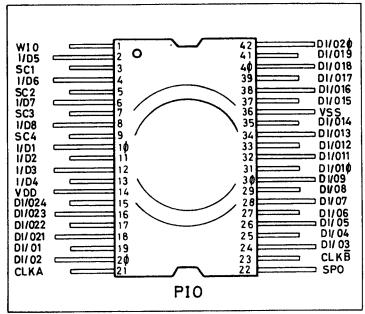

- 3. PIO Circuit of 24 I/O's using all of them as outputs in the following way: 6 as sound control outputs; 10 to control the playfield coils; and 8 to control the playfield registers.

- 4. CPU Central Processing Unit which controls all the surrounding circuits by means of the addressing bus and the Data/Instruction bus. This CPU is described under paragraph 2.3. (Real Structure).

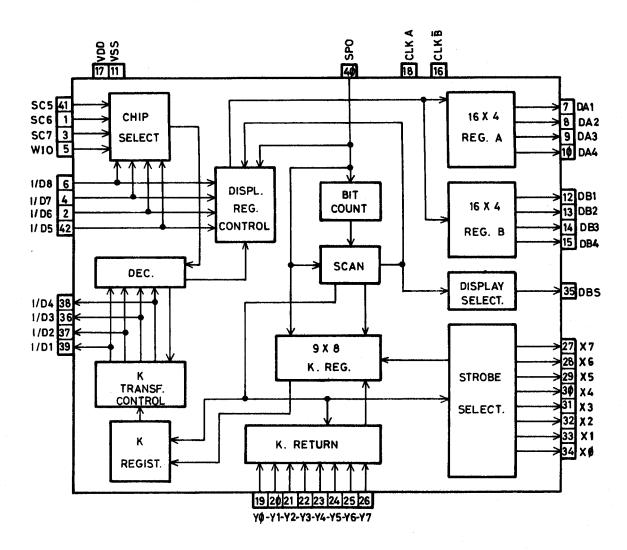

- 5. GPKD This is a control circuit for all the displays and indicating registers housed in the lite—box of the machine.

- 6. and 7. BIC 1 and BIC 2

These are circuits which direct and read the EPROM memory (Gaming program), because the level and form of working of this memory are not directly compatible with the CPU.

- 8. EPROM This is a program memory that contains only those data which refer to each particular model (256 bytes). This memory is recorded by an internal impulse—produced fusion process.

- 9. RAM CMOS An ultra low consumption memory ( < 1  $\mu$ A) which stocks all the data during the time the machine is switched off from the mains. Its power supply meanwhile comes from a small battery which has sufficient charge to maintain the memory active for more than one year. When the machine is switched on, the battery is automatically recharged.

- 10. SOUND SYSTEM This is an assembly comprising 4 TTL chips which generate the sounds and control them by means of the 6 outputs on the PIO (see 3 above).

- 11. MXDR This is a unit mounted on the playfield which, under control from the CPU, selects any of the 40 existing switches. This unit also contains the drivers that control the bumpers and other parts mounted on the playfield.

- 12. DSTR This unit is controlled by the GPKD and activates all the digits and indicators mounted in the lite box of the machine.

- 13. PRINTER Used to print out and change data in the memory.

- NOTE: The main program is distributed in Chips 1 and 2, and comprises a total of 2000 bytes (8 bits per byte), whereas the game program (contained in PROM) consists of only 256 bytes.

#### 2.5 PHILOSOPHY OF SYSTEM III

The functional basis of the system is simple and clearly summarised in the following points:

- a) The entire functioning of the system is controlled and dictated by the Master Unit.

- b) The remaining units are only indicators, or interfaces for these.

- c) If the Master Unit and its power supply voltages are correct, there can only exist the possibility of abnormal functioning if the contact read—out information is defective (in which case all the functions will be carried out well, but in response to contacts which are not relevant for each function).

- d) In order to carry out a proper analysis of the system, it is advisable to consider all the elements which do not belong to the power supply nor Master Unit as indicators. A display is an output indicator which expresses a determined value; a lamp is an output indicator which represents a state, either lit or unlit; a coil is an output indicator which represents a state, either activated or disactivated; a contact is an input indicator which also expresses a state, either open or closed.

On the basis of these considerations we can establish two classes of possible faults: a fault in the actual functioning (Master Unit) and a fault in the indications (easily found by means of the logic detector or test probe).

In order to carry out repairs "in situ", the most practical and rapid means is to substitute the faulty unit for another in proper working order. This is why we have intended and succeeded in producing with the System III a pinball machine where absolutely each and every one of the units are interchangeable, from model to model; including between single and four player games.

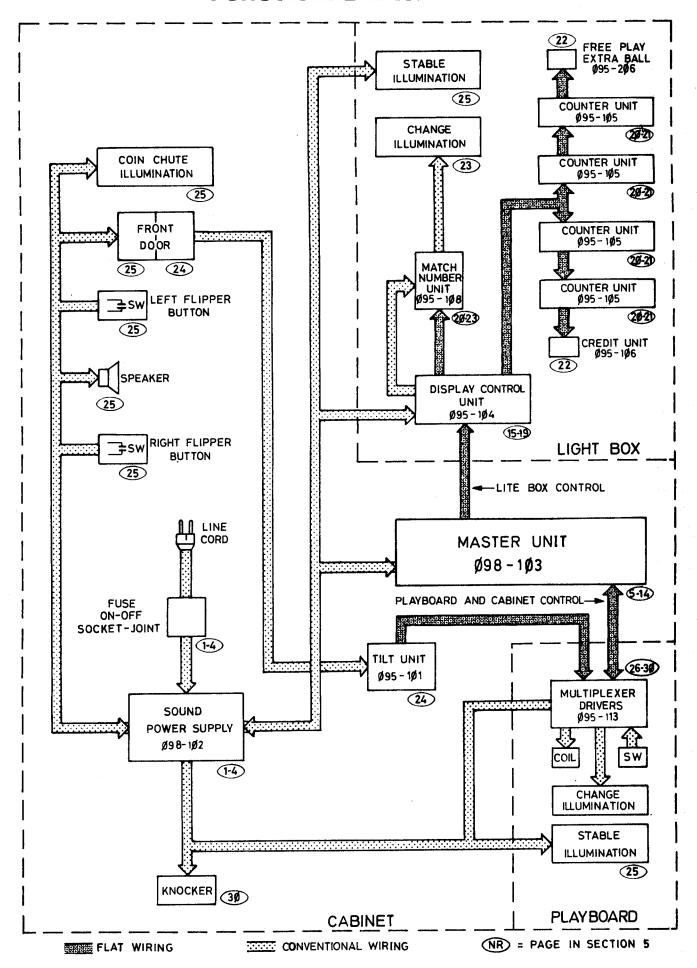

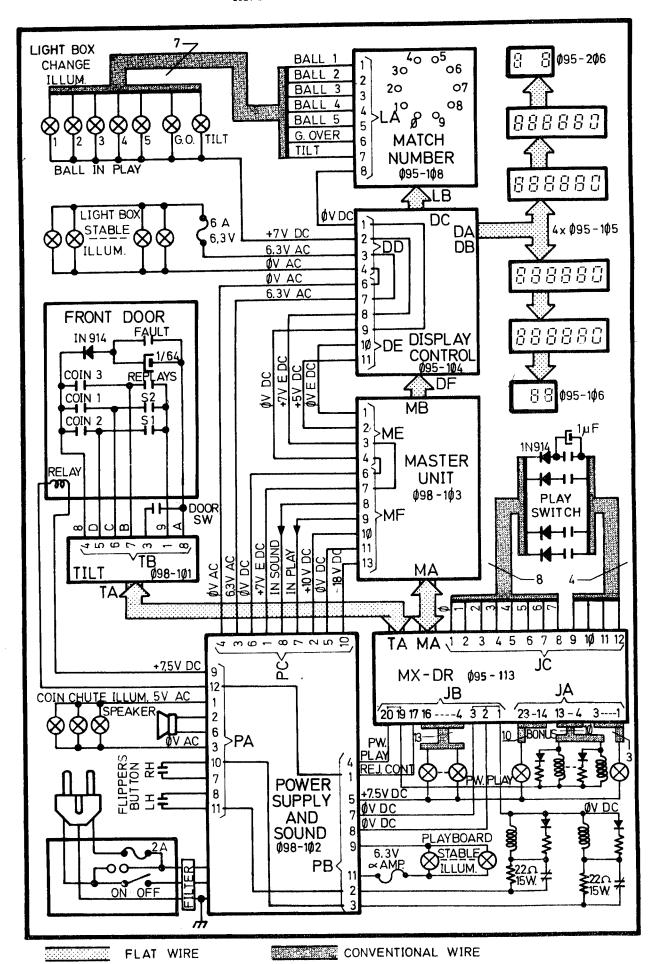

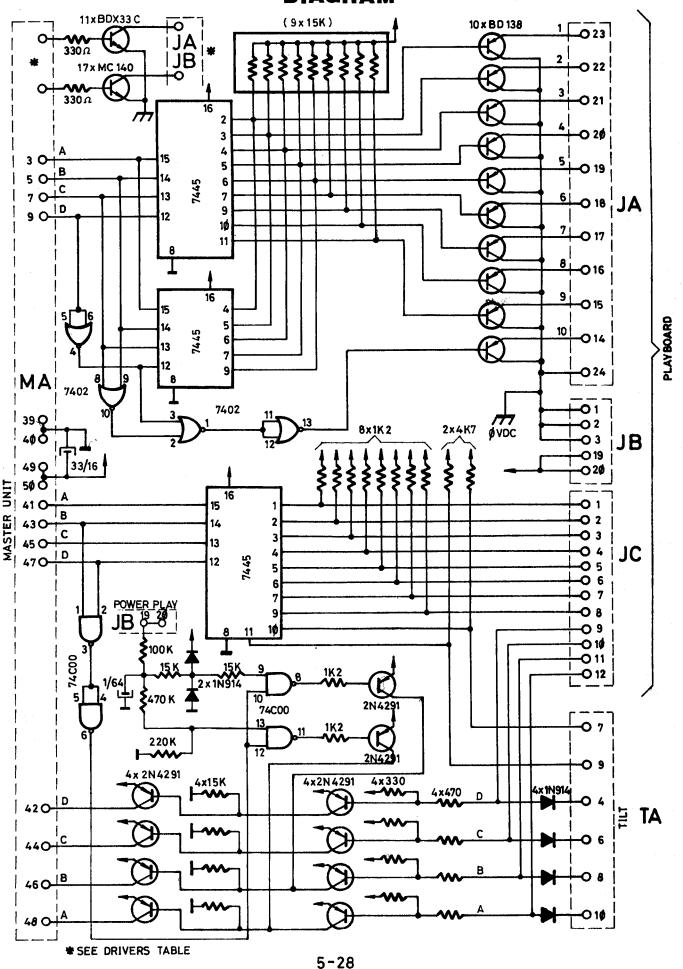

e) In the general diagram (shown below) you can see clearly how the Master Unit controls the rest of the machine via two main ways: lite box control and playboard and cabinet control.

The numbers (N) indicated on this diagram, specify the page number of Section 5 on which each unit is described.

## **FUNCTIONAL DIAGRAM**

## **SECTION 3**

## DESCRIPTION

## **3-1 GENERAL FUNCTIONS**

A normal pinball machine, in the four player version, must offer and offers the following characteristics: coin—slot operation, adjustable tariffs, an indication of the games paid for, four score counters, three or five balls, start button, fault and tilt contacts and indicators, extra ball, free plays obtained from the score (adjustable), match number and flexibility in the system to give any game on the playfield.

The SYSTEM III pinball complies with the above mentioned specification and also offers the following feature:

### 3-2 SELFCHECK

As soon as the machine is connected (using the switch on the right hand underside of the table), a Self-Check routine starts which covers the electric and electronic systems, indicating any fault and identifying the same; if this routine detects a "major" fault (e.g. a short circuit in the coils, driver or I/O RAM failure, etc.), it decides not to continue operating but indicates the fault. Should a "minor" fault be detected (e.g. a coil out, I/O open circuit, short in I/O lamp, etc.), the system will indicate the fault and automatically continue carrying out its function.

The Self-Check routine consists of 6 steps and the results are shown on the display corresponding to Player  $N^{\circ}$  2.

### 1. Lite Box Display and Indicators

All displays and indicators mounted in the lite-box, will be lit up in sequence in all their combinations. When completed, you will see the indication  $\emptyset$   $\emptyset$ .

#### 2. RAM Memory

This function inspects byte by byte all the RAM (shared between the Chips 1 and 2). If everything is in order, you will see the indication 9  $\not \! D$   $\not \! D$ .

If it detects a fault in any of the 256 bytes, it will indicate such a fault in the two digits following the number 9, e.g.: byte 87 is at fault — the system will indicate 9.8.7., in accordance with the hexadecimal code. (Note 1).

3. PIO (Chip controlling Sound, Coil & General Indicators in the Playfield) If everything is in order, this will indicate 8.0.0. If there is a faulty output, it will indicate X.X.X., specifying via the X which is the output concerned, and what is the actual fault.

#### 4. ROM I/O

Two chips incorporating the ROM memory, RAM CMOS control outputs and playfield lamp control outputs. This function analyses one by one all the inputs and outputs. If everything is in order, it will indicate 2.4. . If the fault lies in Chip 1, it will indicate 1.X.X., and if the fault is to be found in Chip 2, 2.X.X. The last two digits indicate the output which is at fault, and the reason why.

#### 5. Sound, Coil Drivers and Coils

This check is made by reading the consumption at the power play supply source, and will indicate, as a "major" fault, the lack of tension, a short circuit in the driver and a short circuit in the coil; and as a "minor" fault, those channels which do not provoke any consumption of the above mentioned supply source (sound, unused channels and drivers or disconnected or cut—off coils). As always the channel and problem will be indicated.

#### 6. RAM CMOS

This function individually checks the 1024 bits in the memory. If all is well, it will indicate 5. $\emptyset$ . $\emptyset$ . If a fault is discovered, it will indicate the byte which is at fault.

If it detects a fault, and when repeating the Self-Check routine it does not indicate the same fault code, the problem is to be found in the stabilization or faulty power supply filter, and the alternative component is the cause of the different readings.

Note 1: If the fault is indicated as 9.7.F or less, this means that the A2361 chip is broken; in all other cases, the problem is to be found in the A2362 chip.

## SELFCHECK TABLE

ALL INDICATIONS ARE IN THE SECOND PLAYER DISPLAY

|      | FUNCTION            |       | OBSERVATIONS                                                                                                                        |

|------|---------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| J, L |                     |       | ODOLINATIONS                                                                                                                        |

| 1    | TEST<br>DISPLAY     | ØØØ   | END OF TEST DISPLAY                                                                                                                 |

| 2    | RAM<br>MEMORY       | 9 X X | FAULT DETECTED. THE LAST TWO DIGITS (1) INDICATE POSITION AT FAULT.                                                                 |

| 2    | R AM<br>MEMORY      | 9 Ø Ø | END OF TEST RAM O.K.                                                                                                                |

| 3    | PIO                 | xxx   | 1ST DIGIT INDICATES GROUP 3-4-5-6-7-8<br>2ND DIGIT INDICATES THE DEFECTIVE BIT * (1)<br>3ND DIGIT INDICATES DEFECTIVE CONFIGURATION |

| 3    | P10                 | 8 Ø Ø | END OF TEST. PIO (O.K)                                                                                                              |

| 4    | ROM I/O             | 1 7 X | SHORT IN OUTPUT X AT-12V (CHIP-1)                                                                                                   |

| 4    | ROM I/O             | 1 4 X | SHORT IN OUTPUT X AT + 5V (CHIP-1) *                                                                                                |

| 4    | ROM I/O             | 2 7 X | SHORT IN OUTPUT X AT -12V (CHIP-2)                                                                                                  |

| 4    | R OM I/O            | 2 4 X | SHORT IN OUTPUT X AT +5V (CHIP-2) *                                                                                                 |

| 4    | ROM I/O             | 2 4   | END OF TEST ROM (O.K)  SHORT TONE   ■                                                                                               |

| 5    | PW. PLAY<br>VOLTAGE | 2 4 6 | VOLTAGE FAULT (POWER PLAY) (1)                                                                                                      |

| 5    | DRIVER              | 2 4 5 | SHORT IN DRIVER (1)                                                                                                                 |

| 5    | COIL                | X 4 7 | COIL X OPEN. / TEST SOUND (X≤5)                                                                                                     |

| 5    | COIL                | X 4 4 | SHORT IN COIL X (1)                                                                                                                 |

| 5    | DR /CL              | 3 Ø Ø | END OF TEST. DR/CL (O.K.) NO MAJOR FAULTS DETECTED                                                                                  |

| 6    | RAM<br>CMOS         | 8 X X | FAULT DETECTED. THE LAST TWO DIGITS (1)                                                                                             |

| 6    | R AM<br>CMOS        | 5 Ø Ø | END OF TEST. CNOS (O.K.)                                                                                                            |

\*IF THE OUTPUT IS OPEN CIRCUITED IT WILL INDICATE +5

(1) MAJOR FAULTS

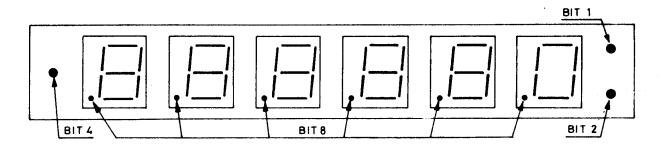

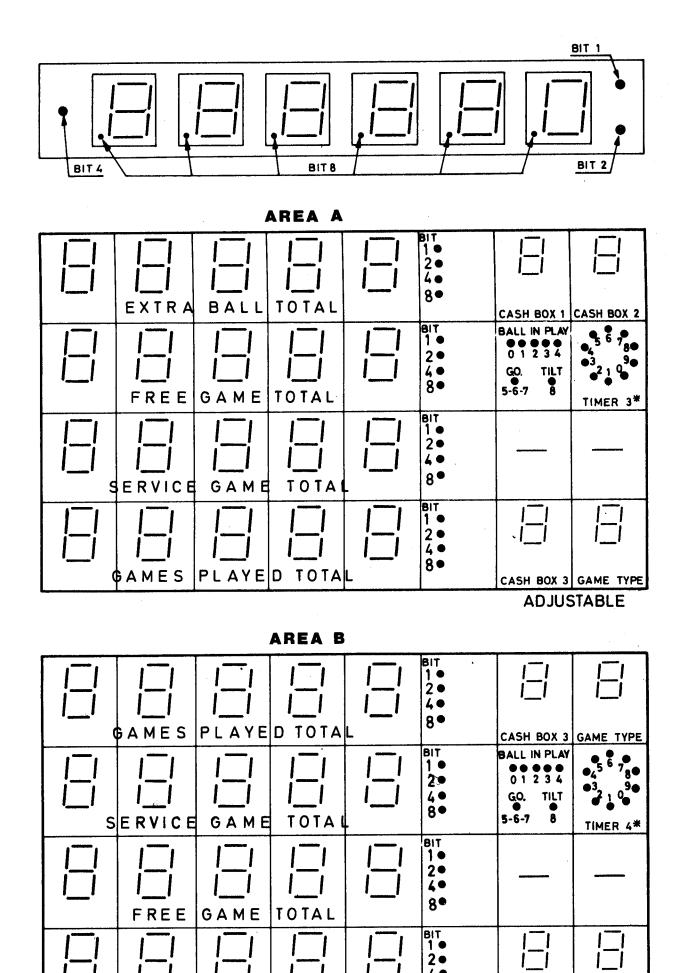

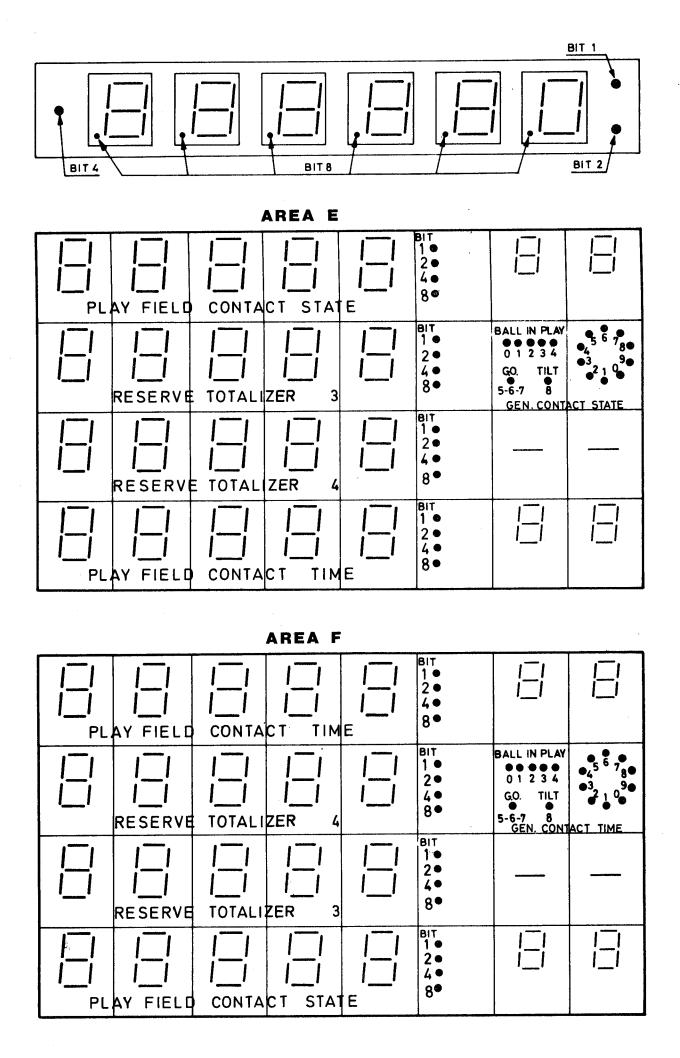

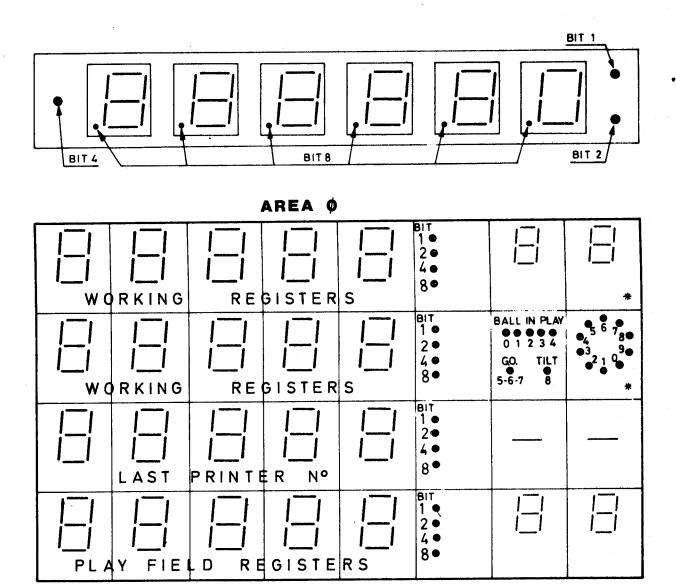

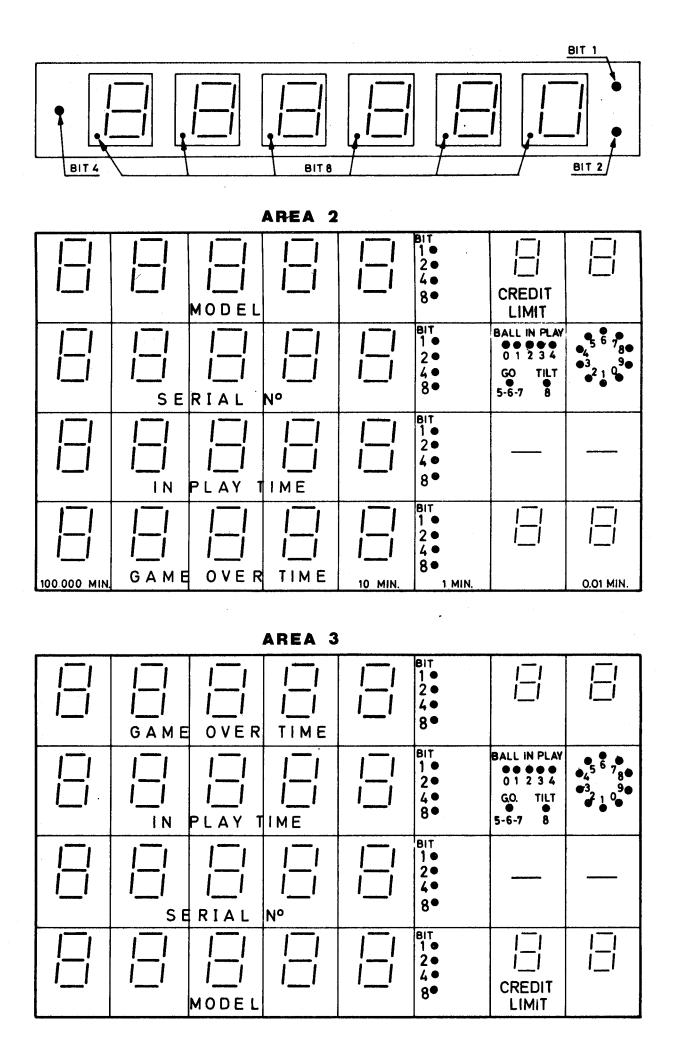

### 3-3 REPRESENTATION AREAS

Areas of Representation for the totalizers and RAM memory registers: As stated before, the SYSTEM III accumulates a quantity of information, up to now unknown in the field of pinball machines. All this information is represented on the displays as follows: whilst the door is shut, the display always represents that shown in Area 4 which corresponds to the actual play data, and when you reach Game Over, it will alternatively flash data on the last score and last handicap (highest score).

On opening the door, the start button will stop working as such and will serve to change the area representation on the displays. There are 16 representation areas on the RAM (see page 3-5). In order to advance from one area to the next, you need only press the button once for each advance of area representation. Whilst the button is pressed down, all the lite box displays will indicate the number of the area which is going to be represented next. Then on releasing the button, the displays will show the data corresponding to each new area. If we press the button just once (starting from area 4), it will stay in area 5 representation, but this will have been inverted; i.e. the information that was previously in the upper displays, will now be shown in the lower displays and vice-versa, (we will understand the advantages of this in the section on ADJUSTMENT).

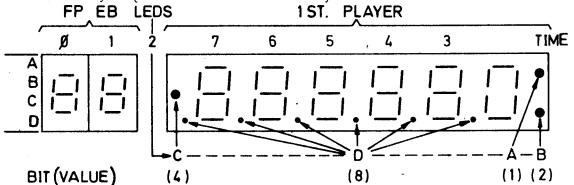

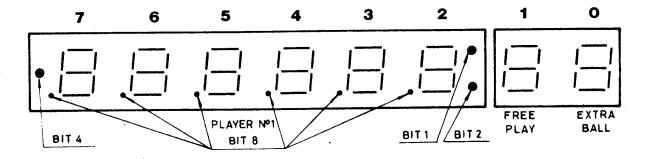

In the representation area £, we can see the state of the playfield contacts, which are indicated in the displays for Free Plays, Extra Ball and 1st Player (see values in the table).

On closing the door, the machine automatically stays ready for play, returning to the preselected area if the door were to be opened again before pressing the start button. When started, the area selected stays at 4.

As can be appreciated, the system provides for a total read—out of the RAM memory. This is why some of the data might be of little interest, with—out full knowledge of the system.

## REPRESENTATION TABLE

| DISPLAY ON          | REPRESENTATION AREAS               | REPRESENTATION AREAS<br>2-6-c-E                |

|---------------------|------------------------------------|------------------------------------------------|

| хх                  | WORKING REGISTERS                  | CREDIT LIMIT X X                               |

| xxxxx               | WORKING REGISTERS                  | MODEL OF GAME *                                |

| x x x x x $\square$ | WORKING REGISTERS                  | SERIAL NUMBER *                                |

| ××××□               | LAST PRINTER CODE                  | TIME IN PLAY (XXXXXX)                          |

| xxxx                | PLAYBOARD REGISTER STATE           | TIME GAME OVER(XXXXXX)                         |

| ××                  | PLAYBOARD REGISTER STATE           | SECONDS TIMER (CENTESIMAL)                     |

| хх                  | FREE PLAY X X EXTRA BALL (COUNTER) | REPLAY PER XXØ.ØØØ                             |

| xxxx                | PLAYER 1 (COUNTER)                 | HANDICAP PLAYER № 1                            |

| ××××□               | PLAYER Nº2 (COUNTER)               | HANDICAF PLAYER Nº 2                           |

| XXXXX               | PLAYER Nº3 (COUNTER)               | HANDICAP PLAYER Nº 3                           |

| XXXXX               | PLAYER Nº4 (COUNTER)               | HANDIÇAP PLAYER №4                             |

| ХХ                  | CREDIT (COUNTER)                   | REPLAY PER XXØØØØ                              |

| хх                  | EXTRA BALL PER XX0,000             | 1 ST COIN X X 2ND COIN REJECTOR(ADJ.)          |

| ××××□               | TOTAL 1 ST COIN REJECTOR           | TOTAL EXTRA BALL                               |

| XXXXX               | TOTAL 2ND COIN REJECTOR            | TOTAL FREE PLAY                                |

| XXXXX               | TOTAL 3RD COIN REJECTOR            | TOTAL PLAY SERVICING                           |

| XXXXX               | DATE OF LAST PRINT-OUT             | TOTAL PLAY METER                               |

| хх                  | FORM OF PLAY*                      | 3RD COIN X X MODE OF REJECTOR (ADJ) PLAY (ADJ) |

| хх                  | PLAYBOARD CONTACTS READ            | PLAYBOARD CONTACTS STATE                       |

| XXXXX               | PLAYBOARD CONTACTS READ            | PLAYBOARD CONTACTS STATE                       |

| XXXXX               | RESERVE TOTALIZER 1*               | RESERVE TOTALIZER 3*                           |

| XXXXX               | RESERVE TOTALIZER 2 *              | RESERVE TOTALIZER 4*                           |

| xxxxx               | PLAYBOARD CONT. DEBOUNCE           | PRESET CONTACTS TIME                           |

| ХХ                  | PLAYBOARD CONT. DEBOUNCE           | PRESET CONTACTS TIME                           |

<sup>\*</sup>SPECIAL GAME SERVICE

### 3-4 HANDICAP

During the time that the machine is at Game Over, the Handicap of each player will be flashed on the displays. It will also be displayed whilst the start button is held down (assuming that the door is closed). The machine leaves the factory with a Handicap for each player of 1.000.000. This value is altered as soon as it is beaten. When the new Handicap exceeds 2.000.000, the respective handicap register stays at 1.000.000, and in this way the machine incorporates an automatic resetting device should the handicap become excessively high.

### 3-5 ADJUSTMENT

There are three RAM memory areas where you will find the various system adjustments.

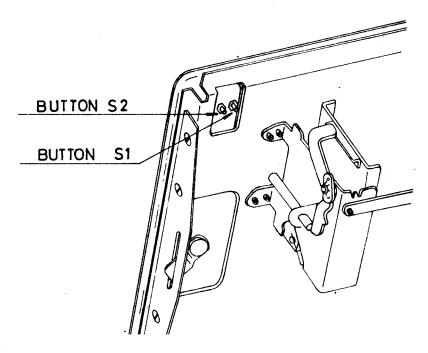

To gain access to alter any of these, simply select the relevant representation area on the credit displays (with the door open and by pressing the start button). When set in this position, press the buttons S1 or S2 which are mounted on the inside of the door, in order to change the left or right hand digits, thereby altering the reading to the desired value. Once the adjustments have been set as required, start the machine in the normal way (with the door shut), so that the new values will have been recorded in the RAM CMOS memory.

## GENERAL ADJUSTMENT TABLE

YOU CAN SEE THIS NUMBER PRESSING THE START BUTTON (IN ALL DISPLAYS)

| سلس  |                   | - YOU CAN SEE THIS NUMBER PRESSING THE START BUTTON (IN ALL DISPLAYS) |                          |                             |  |  |  |  |  |

|------|-------------------|-----------------------------------------------------------------------|--------------------------|-----------------------------|--|--|--|--|--|

| AREA | CREDIT<br>DISPLAY |                                                                       | ADJUSTMENT FUNCTION      |                             |  |  |  |  |  |

| 6    | xx                | REPL                                                                  | REPLAY PER XX0000 POINTS |                             |  |  |  |  |  |

| 7    | xx                | REPL                                                                  | AY PE                    | R XX0000 POINTS             |  |  |  |  |  |

| ٩    | XX                | EXTR                                                                  | A BA                     | ALL PER XX0000 POINTS       |  |  |  |  |  |

| C    | ΧŒ                | 3RD.                                                                  | COIN                     | REJECTOR (X=PLAYS PER COIN) |  |  |  |  |  |

|      | BX                | MODE                                                                  | E OF                     | PLAY (X=A+B+C)              |  |  |  |  |  |

|      |                   |                                                                       | ø                        | EXTRA BALL NOT REPETITIVE   |  |  |  |  |  |

|      |                   | A=                                                                    | 1                        | EXTRA BALL REPETITIVE       |  |  |  |  |  |

|      |                   |                                                                       | 2                        | EXTRA BALL ACCUMULATIVE     |  |  |  |  |  |

|      |                   |                                                                       | ø                        | FREE PLAY NOT REPETITIVE    |  |  |  |  |  |

|      |                   | B=                                                                    | 4                        | FREE PLAY REPETITIVE        |  |  |  |  |  |

|      |                   |                                                                       | Ø                        | 5 BALLS PER PLAY            |  |  |  |  |  |

|      |                   | C=                                                                    | 8                        | 3 BALLS PER PLAY            |  |  |  |  |  |

| 3    | X                 | 1ST COIN REJECTOR (X=8+D+E)                                           |                          |                             |  |  |  |  |  |

|      |                   |                                                                       | ø                        | 1 PLAY                      |  |  |  |  |  |

|      |                   |                                                                       | 1                        | 2 PLAYS                     |  |  |  |  |  |

|      |                   | D=                                                                    | 2                        | 3 PLAYS                     |  |  |  |  |  |

|      |                   |                                                                       | 3                        | 4 PLAYS                     |  |  |  |  |  |

|      |                   | <b>-</b>                                                              | Ф                        | 2 COINS                     |  |  |  |  |  |

|      |                   | E= 4 1 COIN                                                           |                          |                             |  |  |  |  |  |

|      | ■X                |                                                                       |                          | 2ND COIN REJECTOR (X=D+G)   |  |  |  |  |  |

|      |                   | D=                                                                    | SEE F                    | REJECTOR 1                  |  |  |  |  |  |

|      |                   | G=                                                                    | Ø                        | NORMAL PRICE                |  |  |  |  |  |

|      |                   | G=                                                                    | 8                        | PREMIUM PRICE *             |  |  |  |  |  |

<sup>\* 1</sup> EXTRA PLAY WITH 2ND PAYMENT (min. 1 play)

WITHOUT PRESSING THE START BUTTON

(THIS STATE AFFECTS ALL 3 COIN REJECTORS)

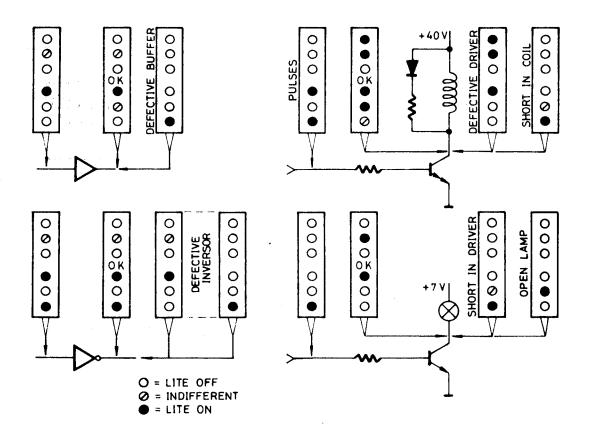

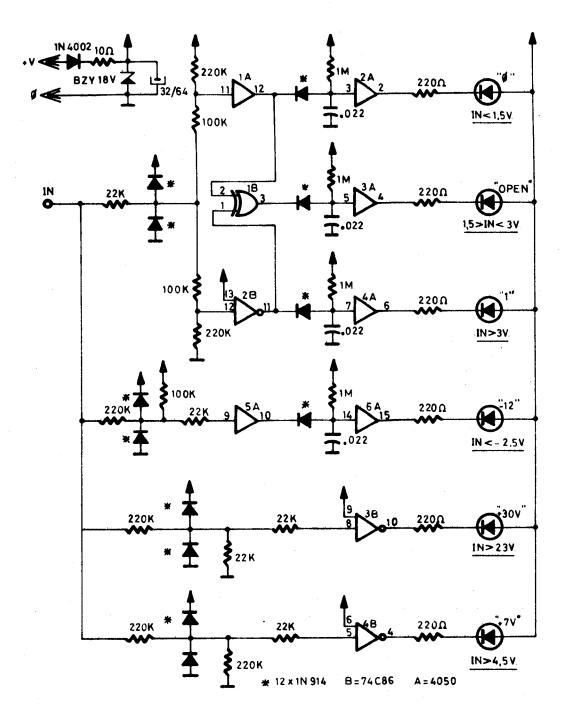

### 3-6 LOGIC DETECTOR

### 094-629

The Test Probe 094-629 is a pulse detector and level indicator which has been designed specially for servicing SYSTEM III.

It contains all the necessary indications for carrying out measurements on any unit and point of the system. This probe 094-629 if used correctly, is the only pocket instrument which makes it possible to find any fault on the system.

The probe cannot take measurements from the mains, for which reason it is recommendable that the service engineer carries a standard multimeter, especially when installing the machine at an unfamiliar site.

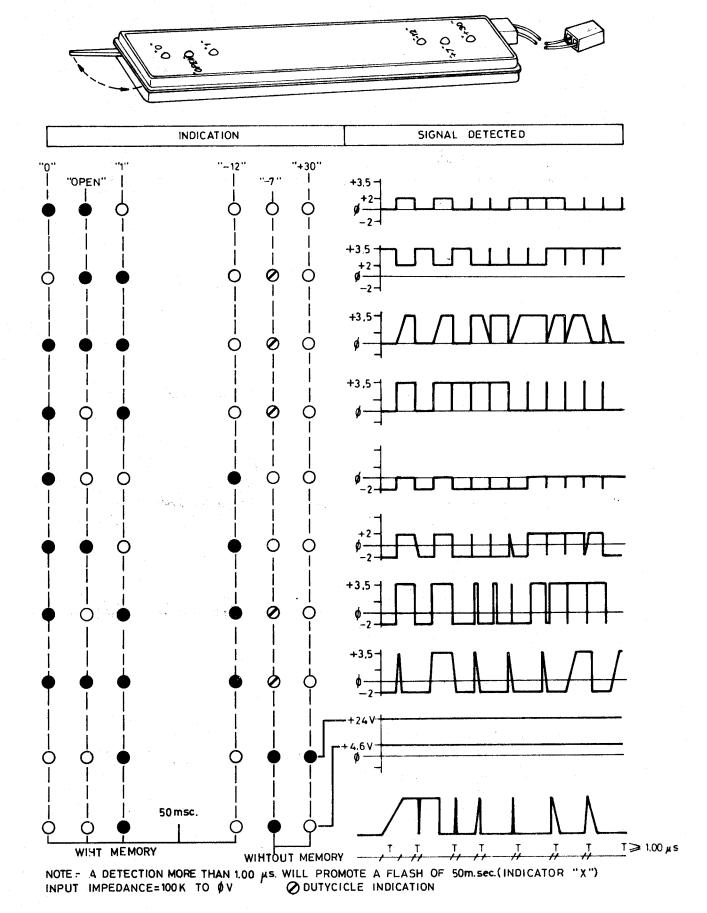

On the enclosed table we have shown the indications given by the test probe, with some types of pulses.

By way of an example, below we are showing the measurements taken on some practical circuits.

Logically these examples are only a sample and the indications in all cases are very easy to interpret. The duty cycle of a signal is in proportion to the brilliance of the LED, denominated +7.

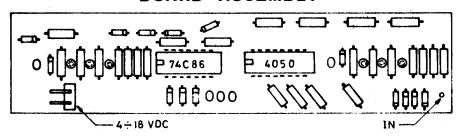

## LOGIC DETECTOR DIAGRAM

### BOARD ASSEMBLY

## LOGIC DETECTOR TABLE

## (LEVEL INDICATOR - PULSE DETECTOR)

### 3-7 MINIPRINTER

Correct use of our Mini-printer, model 2056A, constitutes a really valuable advantage to gain the most from the special characteristics incorporated in the SYSTEM III.

The mini-printer should be used in the following way: firstly, switch off the machine or unplug it from the mains. Secondly, plug in the printer to the socket provided in the Master Unit — connector MD — to be found in the lite box. Replug in the machine and wait for it to finish the Self-Check routine. Check that the resettable date and printer number registers have absorbed the new values correctly; press the start button; switch off or unplug the machine; unplug the printer (all the data is printed out and stored in the printer memory).

If you wish to use the printer merely to obtain data, but without it being necessary to reset any of the registers, then you should not press the start button, but switch off the machine and unplug the printer instead. The data is now in the printer, and the machine registers have not suffered any alteration.

The modifications that the printer creates over the registers and totalizers in the machine are programmed in advance within the printer itself and come into effect when you press the start button, and selecting only the date and coin collection number (if this is the object).

The working printer mode and time are explained in the Master Unit explanation (next Section).

### 3-8 SIMULATION SYSTEM III

The checking Simulator 094-630 makes it possible to check, analyse and simulate all components on our System III electronic pinball. It has an internal capacity to simulate and control 16 games which may be increased by external blocks of 16.

Also it contains the necessary connections to enable the substitution of all parts of the machine and to start functioning any unit of the laboratory.

The Simulator 094-630 is supplied with its own full technical manual.

## **SECTION 4**

### MAINTENANCE

4.1 GENERAL CONDITIONS: The SYSTEM III pinball machines require regular periodic inspection of the conventional electromechanical parts: a) cleaning in general, particularly of the playfield; b) replacement of the rubber rings; c) inspection of the coil stops, plungers, springs, brackets and bumper fittings; d) illumination and indication lamps; e) revision of contacts, running check in presentation area t (see paragraph 4.4).

The actual electronic system does not require routine maintenance, but the service engineers should comply with the following points:

DO NOT CARRY OUT CONNEXIONS, DISCONNEXIONS OR SOLDERING on any part whilst the machine is switched on.

USE THE SELF-CHECK ROUTINE to trace any type of fault that might occur and to repair it.

TO TAKE MEASUREMENTS use a multimeter and our Pulse and Logic Detector (test probe) Ref. 094-629, or its equivalent.

FOR COMPLETE REVISION in a laboratory, the Simulator 096-630 is the only equipment capable of simulating all the functions of the SYSTEM III.

PROBLEMS IN THE POWER SUPPLY: Pull out the PB and PC connector from the supply circuit (with the machine off) and repair the fault, plugging in the connector again (still with the machine off) once you have checked that all voltages are correct.

If maintenance is carried out on the basis of the above hints, you can be sure that the machine will have a virtually limitless life duration.

4.2 COILS: The Self-Check routine detects the two possible faults that could occur in a coil, namely: short or open circuit. If a short circuit is indicated (X.4.4), we suggest you check the relevant diode, connections and mounting (as this fault by itself is almost impossible, and the machine would have detected excess consumption, making the thermal circuit breaker jump). If an open circuit is indicated (X.4.7), the driver and its connections should be checked with the help of the pulse and logic detector (094-629 Test probe), because the Self-Check routine has detected zero consumption.

When replacing a part it is important to ensure correct polarity and proper soldering.

4.3 LAMPS: During the Self-Check routine, a test is made on all outputs (peripherals of the processor) controlling the indicator lamps. This enables, when there is no indication of a fault, to see whether the problem lies in the lamp if this does not lite up, or in the driver if the lamp never goes out.

When replacing a driver or an indicator lamp, a quick check of the relevant connector is recommended.

During the Self-Check routine, all the lamps and indicators in the system will be lit up.

justment) will be shown up in the memory area E; in this area, on the displays corresponding to "free play", "extra ball" and "first player" a permanent and simultaneous reading is obtained of all the contacts in the playfield. Each contact is represented by a digit and a value defined in the corresponding game Service Manual. Each digit can represent the condition of four contacts simultaneously, the value of these being (if they are closed) equal to 1, 2, 4 and 8 respectively, the digit therefore indicates the sum corresponding to the contacts closed.

The following example is given to clarify this point. Four contacts, which we shall call 4A, 4B, 4C and 4D are presented in position 4 (see Fig. 4.1); if 4A and 4B are closed, whilst 4C and 4D are open, the digit will indicate 3; then if 4A is opened, it will indicate 2, and if now 4C is closed, it will show 6. We can thus see that the reading is very straightforward and that the position and value of each contact is implied in its reference number; the first number indicating its position in the display and the second its value. We recommend that the service engineer should familiarize himself with the hexadecimal code and its presentation in the display (see table).

The contacts related to general operations, (start, coin microswitches, tilt fault and selectors 1 and 2) are represented on the indicators corresponding to the Match Number and Game State (Tilt, Game Over or Ball in Play lamps) and their values are as follows:

| FAULT | COIN 1             | COIN 2 | COIN 3 | TILT  | START  | SELECT 1  | SELECT 2          | SWITCH     |

|-------|--------------------|--------|--------|-------|--------|-----------|-------------------|------------|

| 1     | 2                  | 4      | 8      | 1     | 2      | 4         | 8                 | VALUE      |

|       | in Game<br>G.O., B |        |        | Shown | in Mat | ch Number | u <sub>or</sub> Ł | READ<br>IN |

| REPRESENT.<br>CODE                             | ø | 1 | 2 | 3 | 4 | 5 | 6 | .7 | 8             | 9            | 10           | 11           | 12           | 13           | 14           | 15           |

|------------------------------------------------|---|---|---|---|---|---|---|----|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| LAMP LIT                                       | 1 | 2 | 3 | 4 | 5 | G | G | G  | 1 <b>-</b> -T | 2 <b>-</b> T | 3 <b>–</b> T | 4 <b>–</b> T | 5 <b>-</b> T | G <b>-</b> T | G <b>–</b> T | G <b>-</b> T |

| T = Tilt<br>G = Game Over<br>Nº = Ball In Play |   |   |   |   |   |   |   |    |               |              |              |              |              |              |              |              |

Note: The contact for the door and tilt is the same one, and therefore the door has to be open whilst inspecting the areas (contact closed), the reading of this will always be activated.

The playfield contacts are represented in the mentioned area  $\mathbf{E}$ , and in the relevant code the position (digit) is shown quite implicitly, as well as the value for that position. The number indicates the position and the letter shows the value (A = 1, B = 2, C = 4 and D = 8).

#### POSITION

Fig. 4 · 1

For example: Contact 5B will be represented on indicator 5 (thousands unit for the 1st player) by value 2 (if it is closed).

If various contacts are closed at the same position, the value shown would be the sum of the value of each of those contacts.

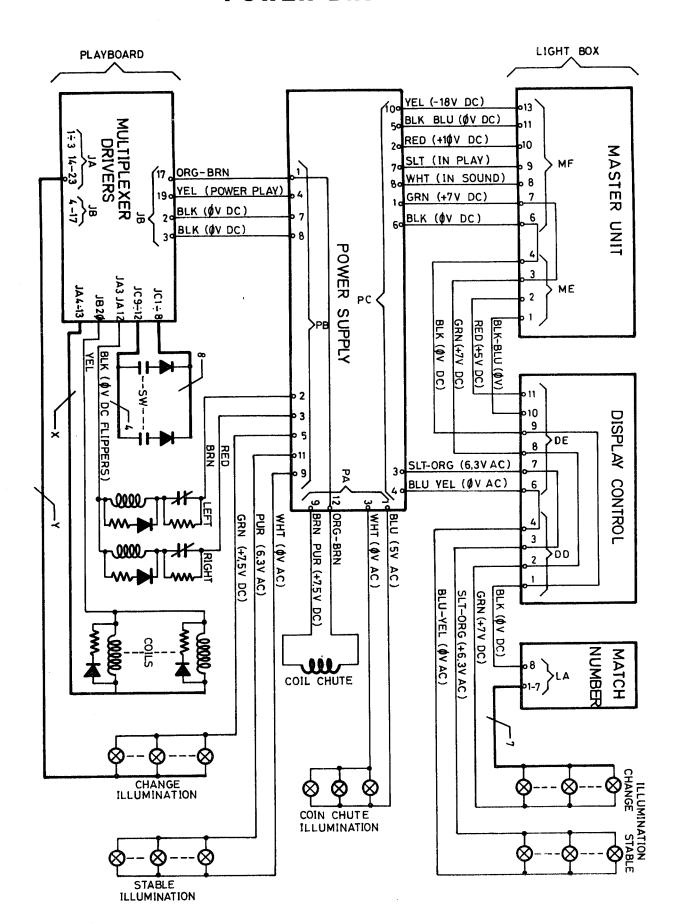

4.5 GENERAL DIAGRAM: The following diagram corresponds to the general schematic of the System III pinball where for greater clarity we have represented in block form the various units which will be described in Chapter 5.

## MACHINE DIAGRAM

The diagram shows all the power supply tensions (conventional wiring) for the various units, and the input and output pins for each of the units. The lines corresponding to the control signals (flat wire), are shown as buses, and their functions are given in the section where we have described the relevant units. In the part representing the playfield, we have shown a couple of lamps and a couple of coils, separated by points, and by this we have wished to show that the exact number of these elements will depend on the game in question, and will be specified in the respective Service Manual for each model. Regarding all the other specific characteristics concerning the playfield, consult the Service Manual for the model in question.

We have also shown all the references for the various unit assemblies.

This diagram corresponds faithfully to the practical make—up of any model of System III pinball, and therefore, it can be regarded as the general schematic, to be used in the analysis, studies and control of the current and future models of games.

## **SECTION 5**

### **MODULES**

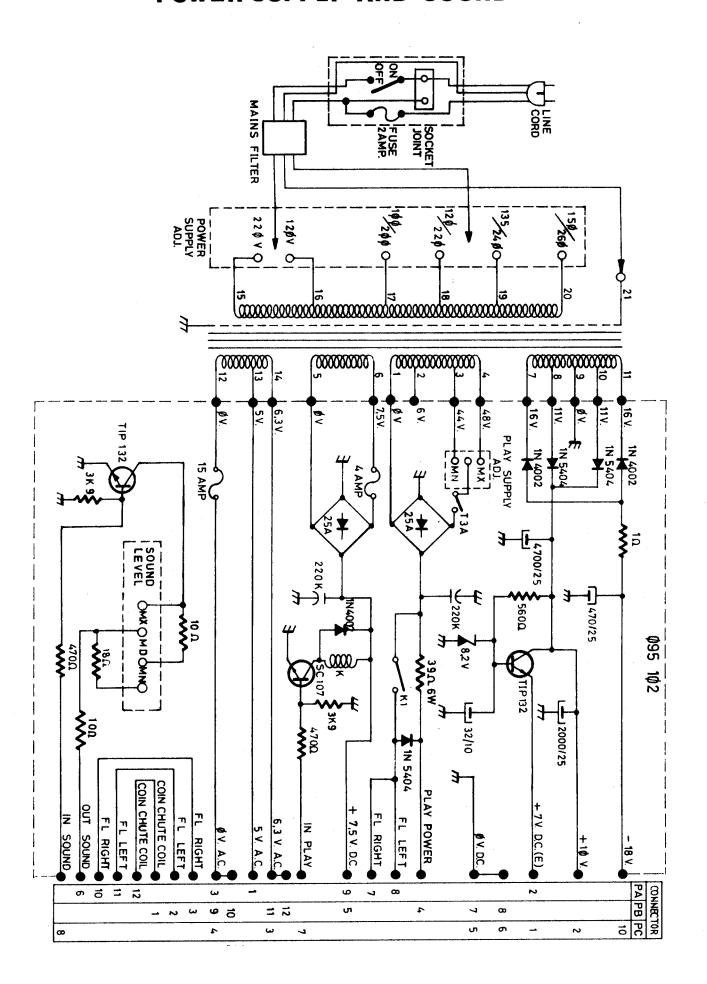

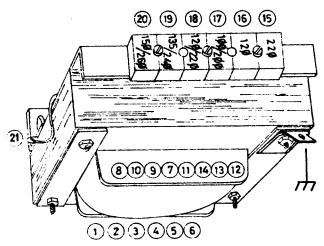

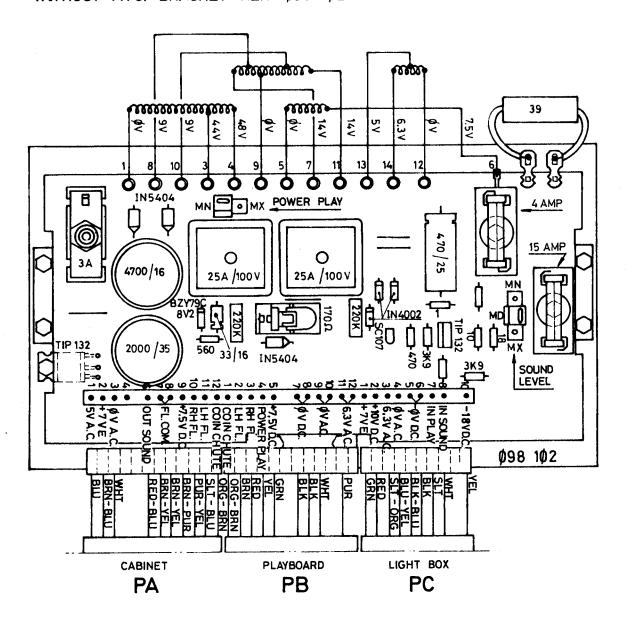

### 5.1 POWER SUPPLY AND SOUND

The power supply board is equipped with a transformer primary with the necessary terminals to allow the machine to work correctly at any mains voltage. The relevant terminal position for 120 volts, covers a range from 90 to 180 volts, and the 220 volt position covers from 180 to 312 v.

| [135 ÷ 18   | <b>Ø</b> 122 ÷ 162 | 1Ø8 ÷ 144   | 9Ø÷12Ø  | RAN         | NGE         |

|-------------|--------------------|-------------|---------|-------------|-------------|

| 150         | 135                | 120         | 1фф     | 12 <b>Ø</b> |             |

| 26 <b>Ø</b> | 240                | 22 <b>0</b> | 200     |             | 22 <b>0</b> |

| 234 ÷ 31    | 2 216 ÷ 288        | 198 ÷ 264   | 180-240 | RAN         | 1GE         |

The secondary positions in the transformer supply the necessary voltages to obtain the following :

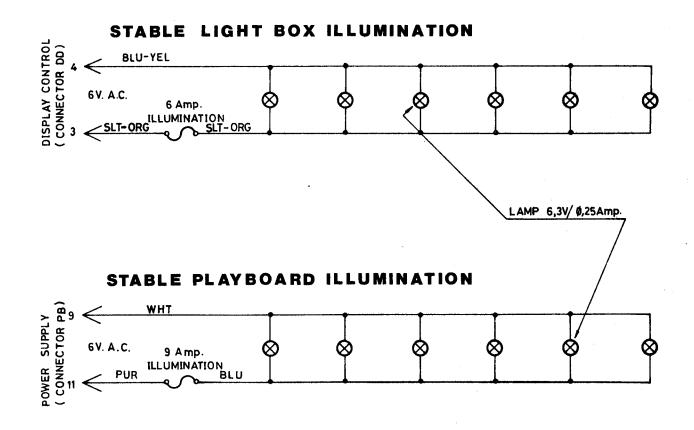

| 5 v. AC       | Lamps for lighting up the coin rejectors               |

|---------------|--------------------------------------------------------|

| 6.3 v. AC     | Stable illumination on the playfield and lite box      |

| + 7.5 v. DC   | Change illumination on the playfield and rejector coil |

| + 7 v. DC (E) | Stabilized display - lite box                          |

| + 10 v. DC    | (with the Master Unit ON) To obtain 5 v. DC stabi—     |

|               | lized current for the electronic logic                 |

| - 18 v. DC    | (with the Master Unit ON) To obtain -12 v. DC stabi-   |

|               | lized current for the MOS circuits                     |

| Power Play    | (adjustable) To feed the playboard coils               |

The Power Play is controlled by the K relay which will cut this power when no "In Play" signal is received. The K contact works in parallel with a 39 ohm. resistor which allows the processor to determine the state of the coils and drivers during the Self-Check routine. This power play is protected by a 3A thermal circuit-breaker with adjustment on the lower side.

The Sound power unit is also to be found in this assembly, and comprises a TIP 132 transistor and a series damper composed of 3 resistors, by means of which the sound level can be adjusted to Maximum (Mx.), Medium (Md.), or Minimum (Mn.).

There is also a series of interconnected pins which allow a better distribution of the cable harness, individualizing the connectors of the Cabinet, Playfield and Lite—box.

## POWER DIAGRAM

### POWER SUPPLY AND SOUND

#### **POWER SUPPLY AND SOUND**

WITH MTG. BRACKET REF. Ø98-1Ø2 WITHOUT MTG. BRACKET REF. Ø95-1Ø2 TRANSFORMER REF. Ø13-3Ø4

#### **MASTER UNIT**

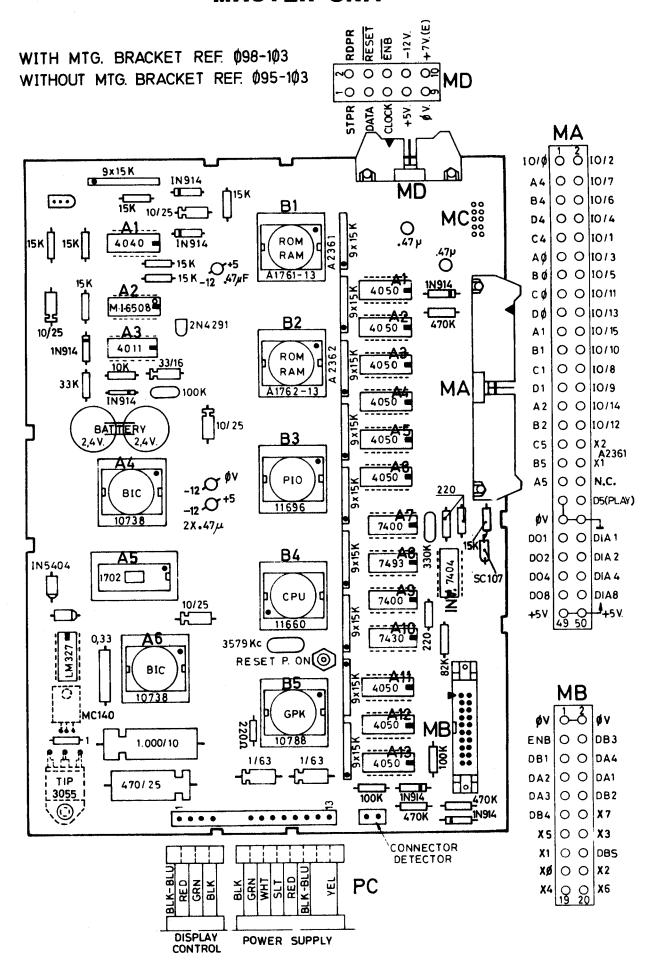

**5.2** The Master Unit needs a working tension of + 10 v. and - 18 v. These voltages are stabilized by the circuit LM 327, which controls a driver MC 140 (output - 12 v. 500 mA max.) and a TIP 3055 (output 5 v. 4 amp max). Both outputs are protected against short circuits, automatically restricting the maximum current to 500 mA and 4 amp respectively, thereby avoiding any destruction of the output transistors should any short circuit occur.

On the tension of + 5 v. and using the union of two F32 diodes, we obtain 6,4 v. which are used to recharge the battery which feeds the RAM CMCS memory HM 6.508-9 and its auxiliary circuits.

If you remove a battery, you will lose the data contained in the RAM. CMOS memory.

The - 12 v. tension is required, along with the + 5 v. tension, in order to work the N-MOS chips existing on the board (CPU, PIO, ROM RAM/I-O, GPKD, BICS and EPPCM).

All the other chips on the board (TTL and Buffer CMOS 4050), as well as those in the Display Control unit and Multiplexer Driver, use only the  $\pm$  5 v. tension.

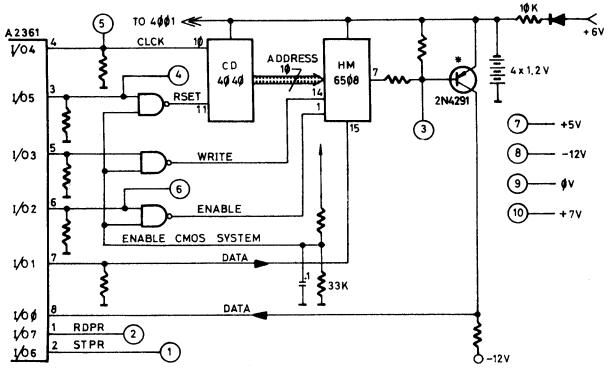

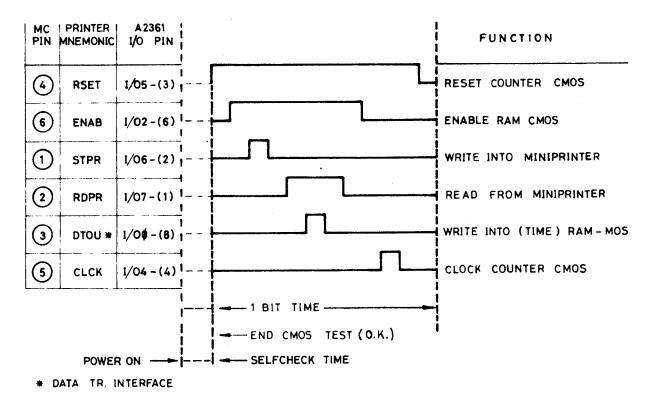

The RAM CMCS memory controlled via the 0-6 outputs on RAM-ROM/I-C 1 (A 2361), and after carrying out all the Self-Check routines, delivers its contents to the working memory RAM (contained in chips A 2361 and A 2362). Then the entire contents of the working memory RAM is again loaded on to the CMOS each time that the machine is at the start position or whenever a ball is introduced into the Ball Return Kicker hole. This means that the RAM CMCS can hold all the definitive data and recover this after a power cut. As a result of this feature, it is possible to control the totalizers, adjustments and other registers in the machine (all contained in the memory), and also check their functioning without suffering alterations. If the machine is switched off after carrying out all the necessary tests, without reaching the start position or ball return state, then the data stored in the CMOS will be the same as before carrying out the tests; none of the test alterations will have been memorized.

Whilst extracting the data from RAM CMOS, this information is transferred to the memory of the "Printer" if this is connected, feeding the working memory RAM with the serial number of the printer in use, and this is then passed or to the RAM CMOS once the start position is reached. Once the Self-Check routine has been completed, the main program begins and the machine is ready for normal functioning.

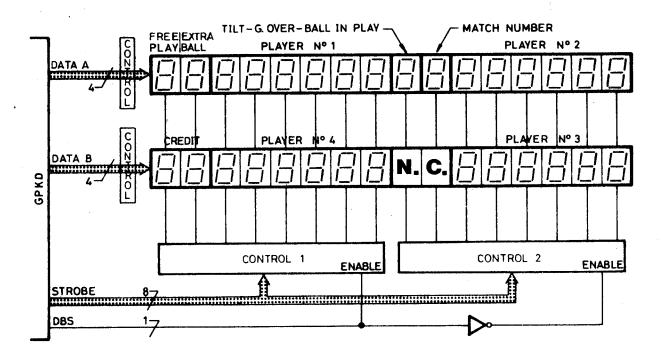

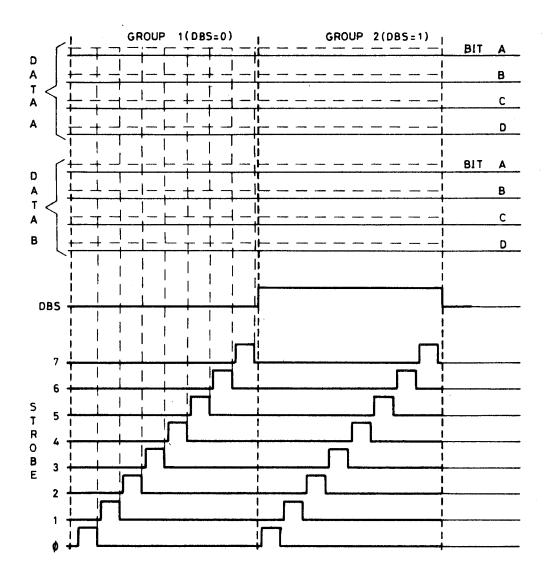

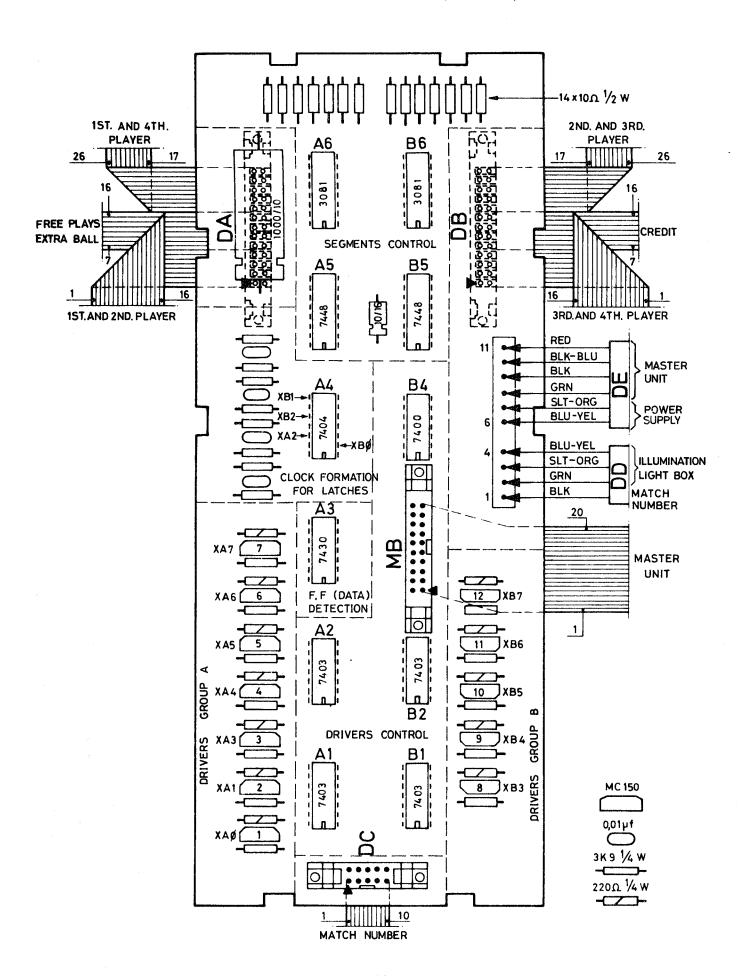

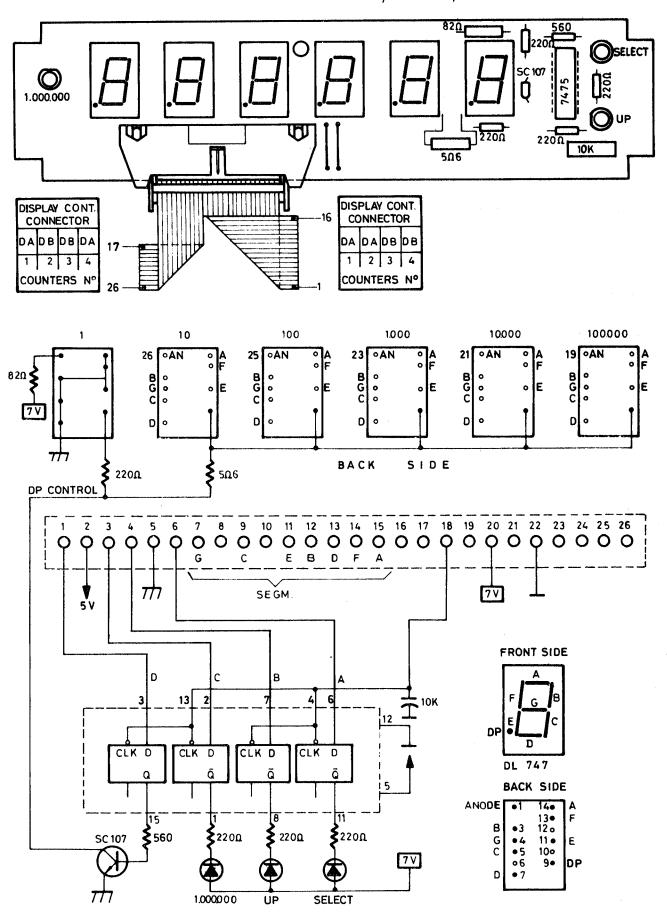

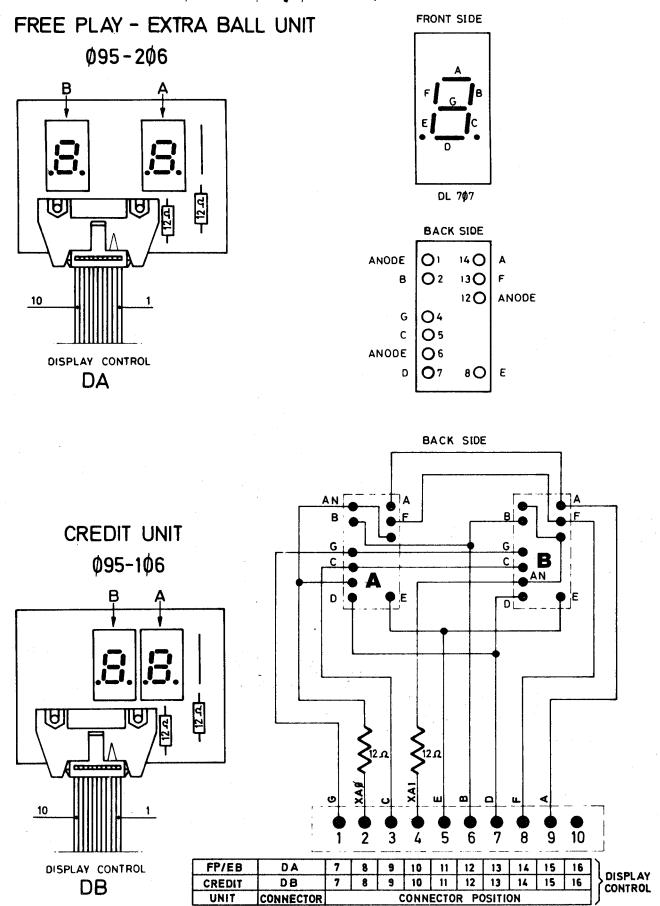

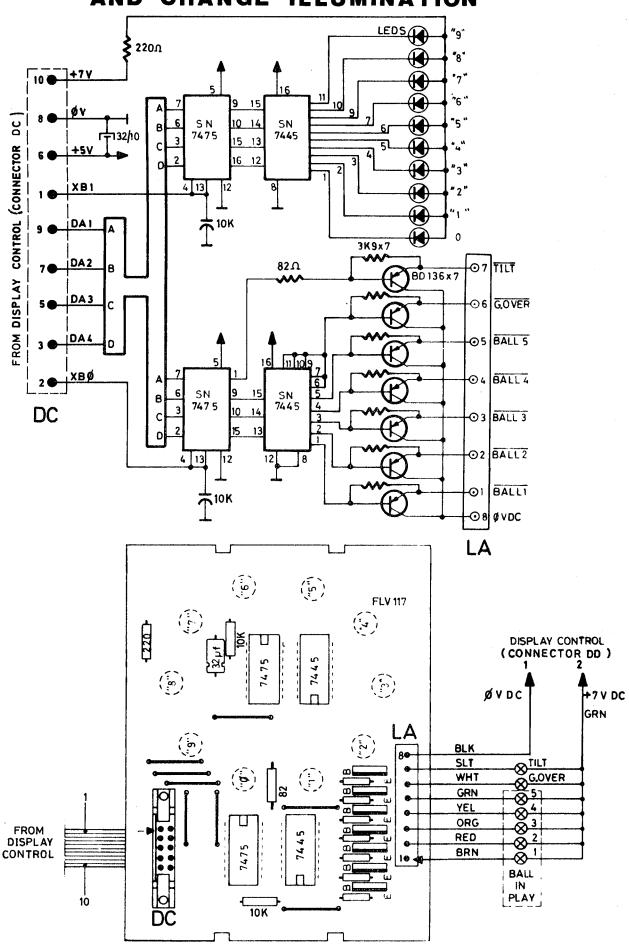

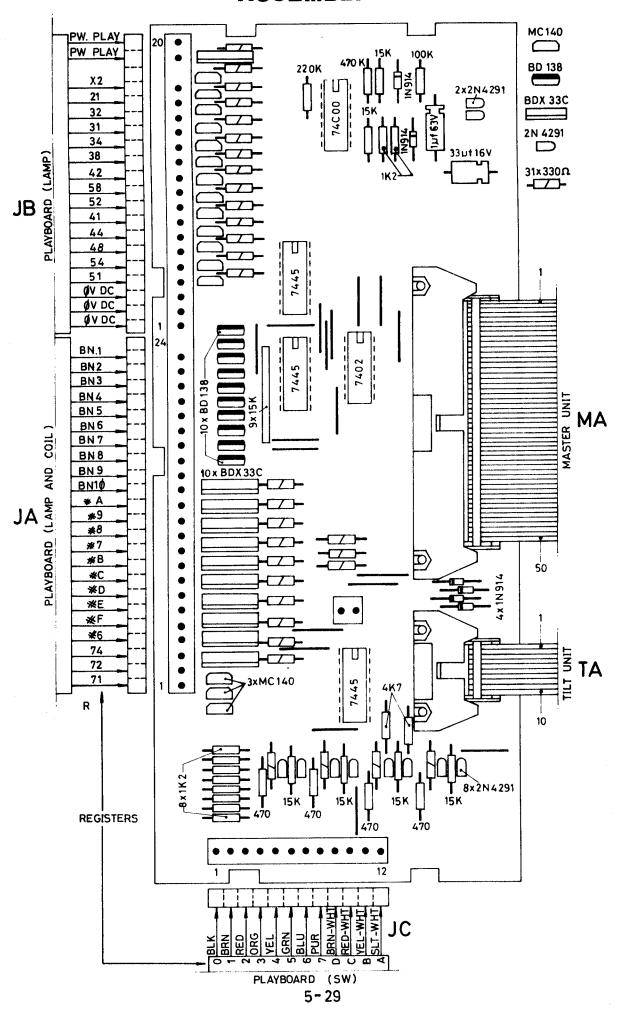

In order to control the indicators in the lite box, a GPKD is used as a peripheral element (display controller), to which all the data contained in the area of the memory selected is trensferred at the rate of 10 times per second; if the front door is closed, the area selection has no effect and the transfer area will be " 4" (play area). By transferring the data at the rate of 10 c/sec., the displays are subject to a smooth but attractive fluctuation.

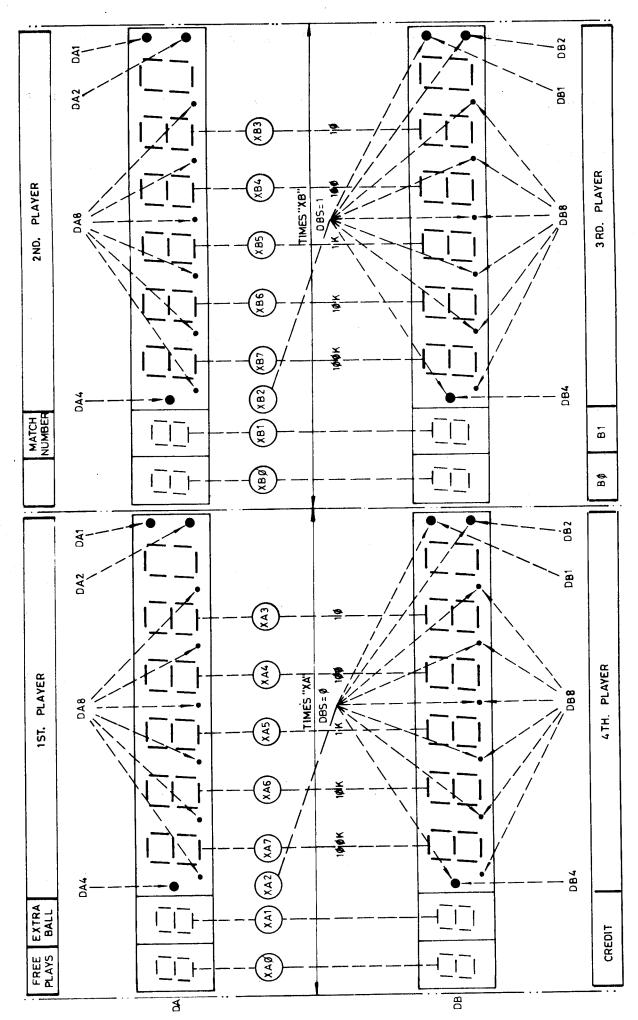

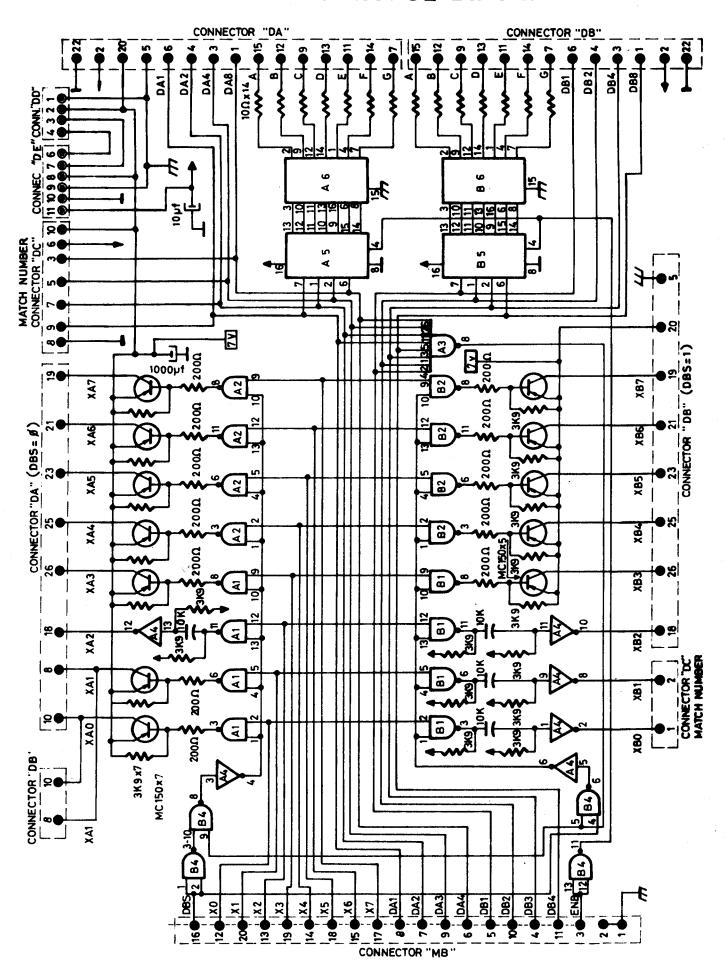

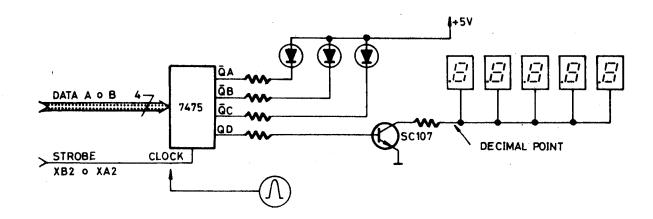

The GPKD feeds the information to the display control unit in two groups of data, each one of them formed by 16 displays or other types of indicator. The column selection is carried out by means of 8 Strobe lines and one group selection.

Control of the playboard elements is carried out by means of the PIO peripheral (programable input—output) and the 16 outputs contained in the ROM—RAM/I—O 2 (A 2362).

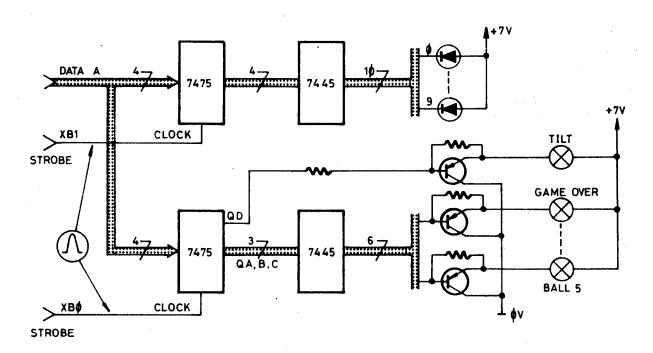

The PIO has 24 outputs; numbers 0 to 5 crntrol the sound circuit, composed of three gates, an oscillator and a TTL counter and mounted on the Master Unit; output Nº 6 controls the Knocker, Nº 7 the Ball Return driver; outputs 8 to 15 are planned to control other electrical elements on the playboard, and outputs 16 to 23 are used to lite up or switch off the playboard indicators (8).

The 16 outputs on the I=0 2 (A 2362) are also planned to control the lites on the playboard.

The I=0 1 (A 2361) is also equipped with 16 inputs-outputs, of which six are used to control the memory RAM CMOS and the Printer whilst the remaining ten are also available to control elements on the playfield. Therefore there is a maximum of 8+8+16+10=42 outputs which can be used for elements and indicators particular to each game.

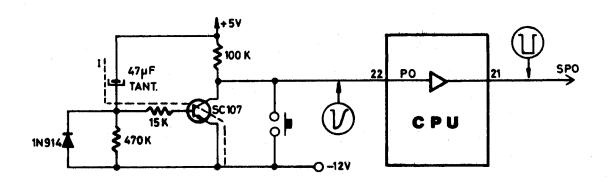

On the Master Unit there is a circuit which will produce a pulse (Reset Power On) when the system is switched on or as a result of a sharp variation of more than  $0.6\ v$ . between the  $+5\ v$ . and  $-12\ v$ . lines. The circuit, functioning and connection can be seen in the next drawing.

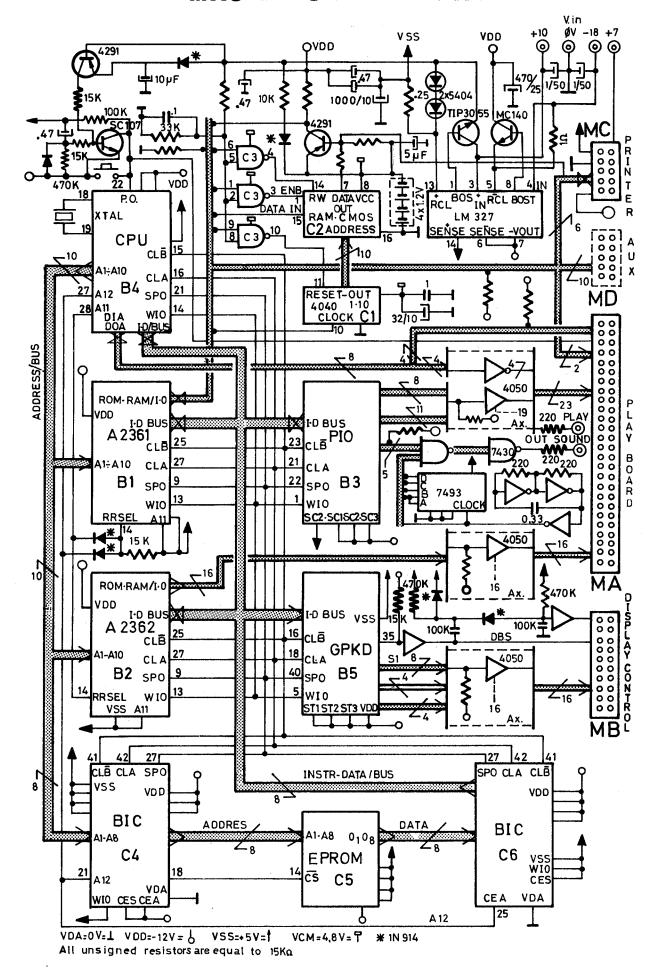

In the diagram shown below, you can see that the CPU controls and addresses all the memories and peripherals, via the address and Instruction—Data buses.

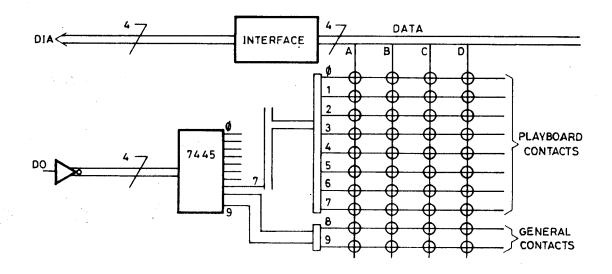

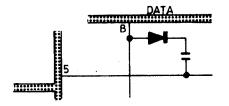

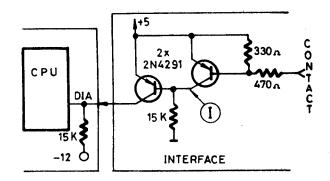

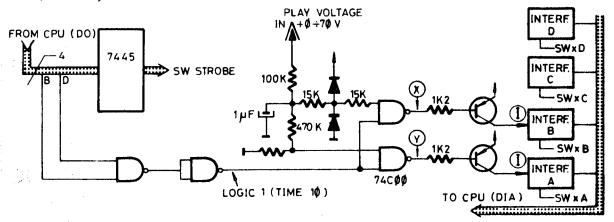

All the contacts are addressed directly by the CPU via their outputs DO, and read by means of their inputs DIA. The contacts are arranged in matrix form of  $16 \times 4$  (maximum of 64 contacts).

As the logic levels of the buses are +5 and -12 volts, and the game memory (EPROM 1702A) is TTL compatible, it is necessary to use 2 BICS (Bus Interface Circuits) in order to make both forms of working competible to each other.

You will see that all the outputs from the Master Unit are protected by an interface (buffer 4050), in order to protect the outputs from the MOS LSI circuits. In the case of the contacts address, the mentioned interface is a chip 7404 (TTL).

The schematic and diagram which we show below, allow you to see the form and times of working and control of the RAM CMOS memory and printer. This routine is carried out at the end of the RAM CMOS test.

N = PIN NUMBER IN MINIPRINTER-SOCKET (MC)NOTE - ALL UNSIGNED RESISTORS ARE OF 15K $\Omega$

#### MASTER UNIT DIAGRAM

#### MASTER UNIT

### MASTER UNIT INTERCONNECTION

| CONNECT.  |            | BUFFER   |           |                                               | MOS           |            |                   |

|-----------|------------|----------|-----------|-----------------------------------------------|---------------|------------|-------------------|

| PIN<br>MA | PIN<br>OUT | POSITION | PIN<br>IN | PIN<br>OUT                                    | TYPE          | REG.       | FUNCTION          |

| 1         | 4          | Α1       | 5         | 8                                             | A 1762-13     | 51         | LITE 51           |

| 2         | 1          | A1       | 3         | 6                                             | A 1762-13     | 54         | LITE 54           |

| 3         | 9          | A5       | 8         | 39                                            | 11696         | 61         | BIT A BONUS       |

| 4         | 15         | A1       | 14        | 1                                             | A 1762-13     | 48         | LITE 48           |

| 5         | 6          | A6       | 7         | 4Ø                                            | 11696         | 62         | BIT B BONUS       |

| 6         | 12         | A1       | 11        | 2                                             | A 1762-13     | 44         | LITE 44           |

| 7         | 12         | A5       | 11        | 41                                            | 11696         | 64         | BIT C BONUS       |

| 8         | 10         | A1       | 9         | 4                                             | A 1762 - 13   | 41         | LITE 41           |

| 9         | 15         | A5       | 14        | 42                                            | 11696         | 68         | BIT D BONUS       |

| 100       | 2          | A2       | 3         | 7                                             | A 1762-13     | 52         | LITE 52           |

| 11        | 12         | A4       | 11        | 19                                            | 11696         | #F         | COIL #F           |

| 12        | 4          | A 2      | 5         | 5                                             | A 176 2-13    | 58         | LITE 58           |

| 13        | 15         | A3       | 14        | 2Ø                                            | 11696         | #E         | COIL #E           |

| 14        | 10         | A2       | 10        | 3                                             | A 1762-13     | 42         | LITE 42           |

| 15        | 15         | A6       | 14        | 24                                            | 11696         | # D        | COIL # D          |

| 16        | 15         | A2       | 14        | 39                                            | A 1762-13     | 38         | LITE 38           |

| 17        | 15         | A4       | 14        | 25                                            | 11696         | #C         | COIL #C           |

| 18        | 12         | A2       | 11        | 37                                            | A 1762 - 13   | 22         | NC.               |

| 19        | 12         | А6       | 11        | 26                                            | 11696         | #B         | COIL #B           |

| 2Ø        | 10         | A2       | 9         | 35                                            | A 1762 -13    | 28         | N.C.              |

| 21        | 6          | A5       | 7         | 27                                            | 11696         | #A         | COIL #A           |

| 22        | 2          | А3       | 3         | 40                                            | A 1762 -13    | 34         | LITE 34           |

| 23        | 10         | A6       | 9         | 28                                            | 11696         | #9         | COIL #9           |

| 24        | 4          | А3       | 5         | 42                                            | A 1762 -13    | 31         | LITE 31           |

| 25        | 4          | Α        | 5         | 29                                            | 11696         | #8         | COIL #8           |

| 26        | 6          | А3       | 7         | 41                                            | A 1762 -13    | 32         | LITE 32           |

| 27        | 2          | A6       | 3         | 3Ø                                            | 11696         | #7         | COIL BALL HOME    |

| 28        | 12         | A3       | 11        | 36                                            | A 1762 -13    | 24         | NC.               |

| 29        | 2          | A5       | 3         | 31                                            | 11696         | #6         | COIL KNOCKER      |

| 3Ø        | 1Ø         | Α3       | 9         | 38                                            | A 1762 - 13   | 21         | LITE 21           |

| 31        | 4          | A4       | 5         | 16                                            | 11696         | 74         | LITE DOUBLE BONUS |

| 3 2       |            |          | _         | 42                                            | · A 1761 - 13 | X2         | REJECTOR CONTROL  |

| 33        | 6          | A4       | 7         | 18                                            | 11696         | 71         | LITE SPECIAL      |

| 34        | _          |          |           | 41                                            | A 1761 - 13   | X1         | EXPANDER MX-DR    |

| 35        | 1Ø         | A4       | 9         | 17                                            | 11696         | 72         | LITE EXTRA BALL   |

| 36        |            | -        |           |                                               |               |            | N.C.              |

| 37        |            |          | _         | _                                             |               |            | ØV(VDA)           |

| 38        | 2          | A4       | 3         | 15                                            | 11696         | 78         | PLAY SIGNAL       |

| 39-4∅     |            |          |           |                                               |               | _          | ØV (VDA)          |

| 41        | 2          | INV 74Ø4 | 1         | 23                                            | 1166Ø         |            | DO 1 BIT A        |

| 42        |            |          |           | 5                                             | 1166Ø         |            | DIA 1 BIT A       |

| 43        | 8          | INV 74Ø4 | 9         | 24                                            | 1166Ø         |            | DO 2 BIT B        |

| 44        |            |          |           | 4                                             | 1166Ø         |            | DIA 2 BIT B       |

| 45        | 4          | INV 74Ø4 | 3         | 25                                            | 1166Ø         |            | DO 3 BITC         |

| 46        |            |          |           | 3                                             | 1166Ø         | ļ <u> </u> | DIA 3 BITC        |

| 47        | 1Ø         | INV 74Ø4 | 11        | 26                                            | 11660         |            | DO 4 BITD         |

| 48        |            |          |           | 2                                             | 1166 Ø        |            | DIA 4 BIT D       |

| 49-5Ø     | <u> </u>   |          | <u> </u>  | <u>l —                                   </u> |               |            | 5 V (VSS)         |

### MASTER UNIT INTERCONNECTION

| 60111507                              |               | DUESED   |          | Mos          |              |                                                  |                        |

|---------------------------------------|---------------|----------|----------|--------------|--------------|--------------------------------------------------|------------------------|

| CONNECT.                              |               | BUFFER   |          | ļ            | MOS          |                                                  |                        |

| PIN                                   | PIN           | DOCITION | PIN      | PIN          | TYPE         | REG                                              | FUNCTION               |

| МВ                                    | OUT           | POSITION | IN       | OUT          | 1Ø788 (GPKD) | Nº                                               | TONCTION               |

| 1                                     |               |          |          |              |              |                                                  | ØV (VDA)               |

| 1                                     |               |          |          |              |              |                                                  | ØV (VDA)               |

| 3                                     | 15            | A 13     | 14       |              |              |                                                  | ENABLE (DISPLAY CONT.) |

| 4                                     | 6             | A 11     | 7        | 14           | 1Ø788 CA     | DB 3                                             | BIT C-DATA GROUP-B     |

| 5                                     | -4            | A 11     | 5        | 12           | 11           | DB 1                                             | BIT A-DATA " B         |

| 6                                     | 2             | A 11     | 3        | 10           | II           | DA4                                              | BIT D-DATA " A         |

| 7                                     | 10            | A 11     | 9        | 8            | II           | DA 2                                             | BIT B-DATA " A         |

| 8                                     | 12            | A 11     | 11       | 7            | II .         | DA 1                                             | BIT A- DATA " A        |

| 9                                     | 15            | A 11     | 14       | 9            | 11           |                                                  | BIT C-DATA " A         |

| 10                                    | 6             | A 12     | 7        | 13           | 11           |                                                  | BIT B-DATA " B         |

| 11                                    | 4             | A 12     | 5        | 15           | 11           |                                                  | BIT D-DATA " B         |

| 12                                    | 2             | A 12     | 3        | 27           | 11           | X7                                               | STROBE TIME X7         |

| 13                                    | 10            | A 12     | 9        | 29           | . 11         | X5                                               | STROBE TIME X5         |

| 14                                    | 12            | A 12     | 11       | 31           | 11           | X3                                               | STROBE TIME X3         |

| 15                                    | 15            | A 12     | 14       | 33           | 11           |                                                  | STROBE TIME XI         |

| 16                                    | 6             | A 13     | 7        | 35           | 11           | DBS                                              | SELECT. GROUP          |

| 17                                    | 4             | A 13     | 5        | 34           | 11           | XØ                                               | STROBE TIME XO         |

| 18                                    | 2             | A 13     | 3        | 32           | II.          | X2                                               | STROBE TIME X2         |

| 19                                    | 10            | A 13     | 9        | 3Ø           | 11           | X4                                               | STROBE TIME X4         |

| 20                                    | 12            | A 13     | 11       | 28           | 11           | X6                                               | STROBE TIME X6         |

|                                       | 1             |          | 1        | 1            | 11           |                                                  | SC6 TO-12V             |

|                                       | †···          |          |          | 2            | 10           | 1/D6                                             | TO INST. BUS           |

|                                       | 1             |          |          | 3            | li .         |                                                  | SC7 TO -12V            |

|                                       | <b>†</b>      |          | 1        | 4            | 11           |                                                  | TO INST. BUS           |

|                                       |               |          |          | 5            | 11           | W/I-O                                            | TO INST.BUS            |

|                                       |               |          |          | 6            | 11           | 1/D8                                             | TO INST. BUS           |

|                                       | 1             |          |          | 11           | lı .         |                                                  | 5V VSS                 |

|                                       |               |          |          | 16           | 11           | CLKE                                             | CLOCK B                |

| · · · · · · · · · · · · · · · · · · · |               |          |          | 17           | II.          |                                                  | -12 (VDD)              |

|                                       |               |          |          | 18           | lt .         | CLKA                                             | CLOCK A                |

|                                       |               |          |          | 19           | ll ll        | NC                                               |                        |

|                                       |               |          |          | 20           | 11           | NC                                               |                        |

|                                       |               |          |          | 21           | II .         | NC                                               |                        |

|                                       |               |          |          | 22           | II .         | NC.                                              |                        |

|                                       |               |          |          | 23           | 11           | NC                                               |                        |

|                                       |               |          |          | 24           | И            | NC                                               |                        |

|                                       |               |          | <u> </u> | 25           | II           | NC                                               |                        |

|                                       |               |          |          | 26           | 11           | NC                                               |                        |

|                                       |               |          |          | 36           | II           |                                                  | INST. BUS              |

|                                       |               |          | <u> </u> | 37           | 11           |                                                  | INST. BUS              |

|                                       | <u> </u>      |          | <b></b>  | 38           | 11           |                                                  | INST. BUS              |